Zou. Yida

ProQuest Dissertations and Theses; 1999; ProQuest Dissertations & Theses Global

### **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps. Each original is also photographed in one exposure and is included in reduced form at the back of the book.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

$\mathbf{UMI}^{^{\mathbf{n}}}$

Bell & Howell Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

# **NOTE TO USERS**

Page(s) not included in the original manuscript are unavailable from the author or university. The manuscript was microfilmed as received.

85

This reproduction is the best copy available.

**UMI**

# APPLICATION OF SILICON PIEZORESISTIVE STRESS TEST CHIPS IN **ELECTRONIC PACKAGES**

Yida Zou

A Dissertation

Submitted to

The Graduate Faculty of

Auburn University

In Partial Fulfillment of the

Degree of

Doctor of Philosophy

Auburn, Alabama

August 30, 1999

UMI Number: 9939651

UMI Microform 9939651 Copyright 1999, by UMI Company. All rights reserved.

This microform edition is protected against unauthorized copying under Title 17, United States Code.

300 North Zeeb Road Ann Arbor, MI 48103

# APPLICATION OF SILICON PIEZORESISTIVE STRESS TEST CHIPS IN **ELECTRONIC PACKAGES**

Yida Zou

Certificate of Approval:

Richard Calager, Co-Chairman Distinguished University Professor Electrical and Computer Engineering

Jeffre C. Suhling, Co-Chairman Associate Professor

Mechanical Engineering

Hareesh V. Tippur Associate Professor

Mechanical Engineering

Alumni Professor

Electrical and Computer Engineering

Graduate School

#### **VITA**

Yida Zou, Daughter of Fazhi Zou and Jieming Zhong, was born on March 20, 1966, in Guixian, Guangxi Province, China. She graduated from Yanban second High School, in Yanji, Jilin Province, China, in 1984. She went to East China Institute of Technology in Nanjing, and graduated with the degree of Bachelor of Mechanical Engineering in July of 1988. She entered the graduate program in East China Institute of Technology immediately, and received her Master of Science in Mechanical Engineering in March of 1991. After her graduation, she joined the faculty of the Mechanical Engineering Department of East China Institute of Technology, and performed her teaching and research duties in the area of structural design, finite element analysis, and experimental mechanics. She started her Ph.D. program in the Mechanical Engineering Department, Auburn University, Alabama, in March 1995.

#### **DISSERTATION ABSTRACT**

# APPLICATION OF SILICON PIEZORESISTIVE STRESS TEST CHIPS IN ELECTRONIC PACKAGES

#### Yida Zou

Doctor of Philosophy, August 30, 1999 (M. S., East China Institute of Technology, 1991) (B. S., East China Institute of Technology, 1988)

#### 316 Typed Pages

Directed by Jeffrey C. Suhling and Richard C. Jaeger

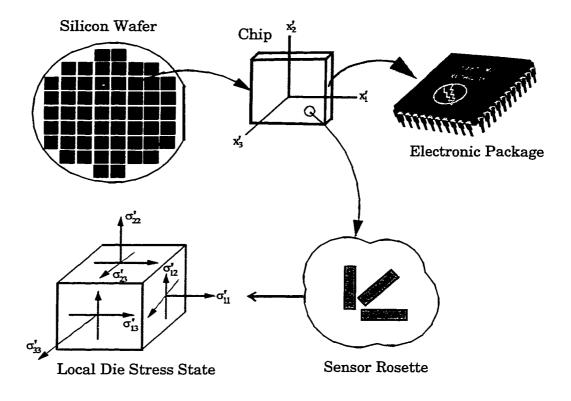

In this work, both special (100) and (111) silicon test chips containing an array of optimized piezoresistive stress sensor rosettes have been successfully applied within several electronic packaging configurations. Unlike (100) silicon test chips, (111) silicon test chips are able to measure the complete stress state on the die surface. After calibration and characterization of the test chips, they were packaged into various assemblies. The post packaging resistances of the sensors were then recorded at room temperature, as a function of temperature excursion, and during long term packaging reliability qualification tests (thermal cycling and thermal aging). The stresses on the die surface were calculated using the measured resistance changes and the appropriate theoretical equations. For comparison purposes, three-dimensional nonlinear finite element simulations of the

packaging processes were also performed, and the stress predictions were correlated with the experimental test chip data.

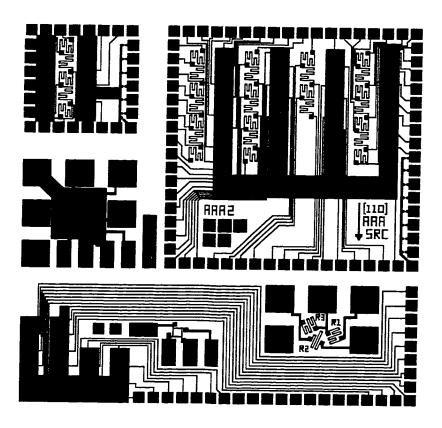

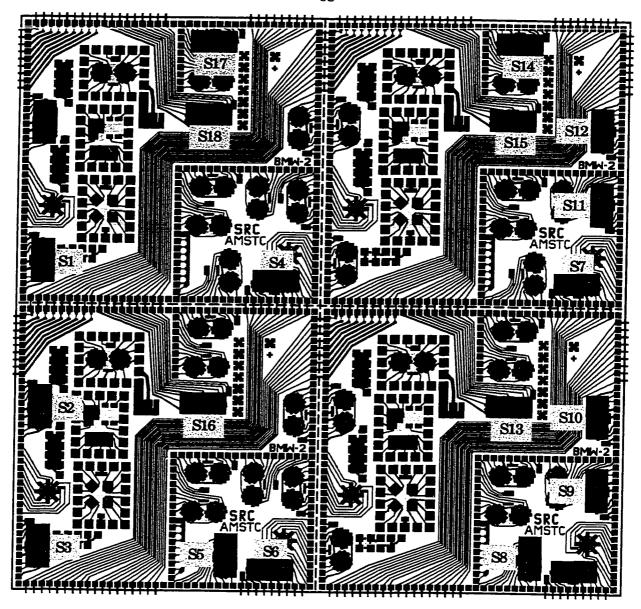

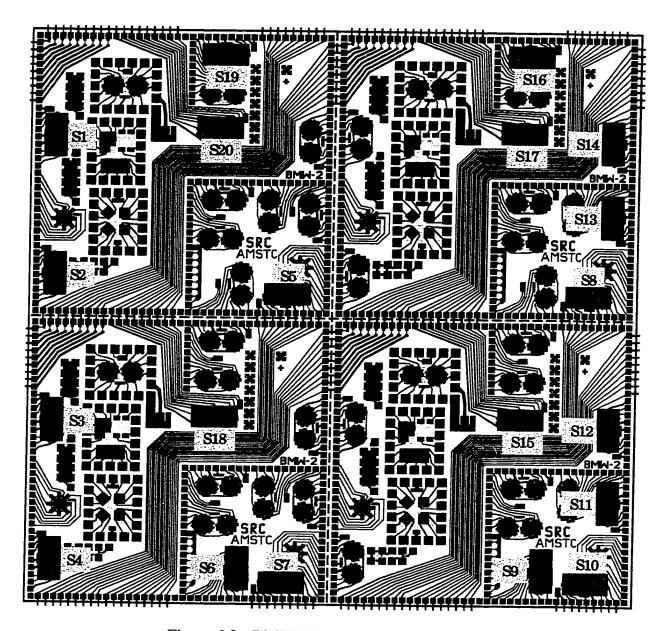

AAA2 (100) silicon test chips containing optimized four element dual polarity rosettes have been applied within 44 pin Plastic Leaded Chip Carrier (PLCC) packages and 240 pin Quad Flat Packs (QFP's). In these plastic package experiments, comparison of the stress levels induced by various molding compounds was emphasized. Advanced (111) silicon test chips (BMW-1 or BMW-2) comprising an array of optimized eight-element dual polarity piezoresistive sensor rosettes were encapsulated in 240 pin QFP's, 160 pin QFP's, Chip on Board (COB) packages, and 281 pin ceramic Pin Grid Array (PGA) packages. In addition to molding compound evaluations, BMW-1 test chips encapsulated in 240 pin QFP's were used to detect the presence of delaminations between the die surface and the encapsulant. In the wire bonded COB package studies, die surface stress evaluations were conducted after die attachment, and throughout the cure cycle of the liquid encapsulant. The stresses were also studied as a function of temperature, and then measured during reliability testing (thermal cycling and high humidity storage). Furthermore, a comparison of COB stress levels obtained with convection and variable frequency microwave encapsulant curing was performed. Finally, stress levels were evaluated within 281 pin ceramic PGA packages using high temperature die-attachment materials. Variations in the package stress levels were monitored during thermal cycling and thermal aging reliability tests.

#### **ACKNOWLEDGMENTS**

The Author would like to thank her advisor Dr. Jeffrey C. Suhling and co-advisor Dr Richard C. Jaeger for their directions, patience and encouragement. Many thanks to Dr. Wayne R. Johnson for his help in Chip-On-Board experiments and his valuable suggestions. The author would like to thank Charles D. Ellis for his help in preparing the test chips and printed circuit boards. Thanks are also due to Michael J. Palmer for his effort to pursue perfect wire bonding work for Chip-on-Board samples, to William Leo Baugh for his in time repair of automated probe station. The author would like to thank her colleague Ahsan Mian for test chip calibration results, and Ted Lin, Steve Suh, Yanling Kang and Ray Moral for their sincere help. The author also wishes to thank the Semiconductor Research Corporation (SRC) and the Alabama Microelectronics Science and Technology Center (AMSTC) for their financial support during this research.

The author would like to thank all her friends for their supports and understanding during this four and half years. Finally, many thanks go to her parents Fazhi Zou, and Jieming Zhong, and her two sisters for their love as a family.

| Style manual or journal used Guide to Preparation and Submission of Theses and |

|--------------------------------------------------------------------------------|

| Dissertations                                                                  |

| Computer software used Microsoft Word 97                                       |

|                                                                                |

## TABLE OF CONTENTS

| LIST ( | FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                      | хi   |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| LIST   | TABLES                                                                                                                                                                                                                                                                                                                                                                                                                       | viii |

| 1      | NTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                  | 1    |

| 2      | ITERATURE REVIEW                                                                                                                                                                                                                                                                                                                                                                                                             | 9    |

| 3      | EVIEW OF PIEZORESISTIVE THEORY  1 General Resistance Change Equations 2 Resistance Change Equations for Silicon Wafer Planes                                                                                                                                                                                                                                                                                                 | 20   |

| 4      | PTIMIZED PIEZORESISTIVE SILICON TEST CHIPS  (100) Silicon Test Chip (AAA-2)  (111) Silicon Test Chips (BMW-1 and BMW-2)  4.2.1 Optimized Eight Element Rosette  4.2.2 Auburn BMW-1 Silicon Test Chip  4.2.3 Auburn BMW-2 Silicon Test Chip  4.2.4 TCR Mismatch Analysis  Test Chip Application Procedure  4.3.1 Initial Resistance Characterization  4.3.2 Packaging Assembly  4.3.3 Resistance Measurements after Packaging | 31   |

| 5      | HARACTERIZATION OF PLASTIC PACKAGES  Introduction  44 Pin PLCC Packages - (100) AAA-2 Test Chips  5.2.1 Packaging Studies  5.2.2 Experimental Results and Comparison with FEM Predictions  160 Pin QFP Packages - (111) BMW-2 Test Chips  5.3.1 Packaging Studies  5.3.2 Experimental Results and Comparison with FEM Predictions  Summary                                                                                   | 72   |

| 6      | HREE DIMENSIONAL DIE SURFACE STRESS IEASUREMENTS IN DELAMINATED AND ON-DELAMINATED 240 PIN QFP'S 1 Introduction                                                                                                                                                                                                                                                                                                              | 97   |

|      | 6.2   | Stress Measurements in Non-Delaminated Packages 6.2.1 Packaging Studies - (100) Silicon AAA2 Test Chips 6.2.2 Packaging Studies (111) Silicon PAGE Chips |     |

|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | 6.3   | 6.2.2 Packaging Studies - (111) Silicon BMW-2 Test Chips<br>Stress Measurements in Delaminated Packages - (111) Silicon<br>BMW-1 Test Chips              |     |

|      | 6.4   | Summary                                                                                                                                                  |     |

| 7    |       | TTU STRESS STATE MEASUREMENTS DURING P-ON-BOARD ASSEMBLY Introduction                                                                                    | 131 |

|      | 7.1   | Chip-on-Board Packaging Studies                                                                                                                          |     |

|      | 7.3   |                                                                                                                                                          |     |

|      | 7.4   |                                                                                                                                                          |     |

|      | 7.5   | Stress Variation During Encapsulant Cure                                                                                                                 |     |

|      | 7.6   | · · · · · · · · · · · · · · · · · · ·                                                                                                                    |     |

|      | 7.7   | Summary                                                                                                                                                  |     |

| 8    | COM   | PARISON OF CHIP-ON-BOARD STRESS LEVELS WITH                                                                                                              |     |

|      | CON   | VECTION AND VARIABLE FREQUENCY MICROWAVE                                                                                                                 |     |

|      |       | APSULANT CURING                                                                                                                                          | 171 |

|      | 8.1   | Introduction                                                                                                                                             |     |

|      | 8.2   |                                                                                                                                                          |     |

|      | 8.3   | Stress Due to Die Attachment                                                                                                                             |     |

|      | 8.4   | Stress Variation During Encapsulant Cure                                                                                                                 |     |

|      | 8.5   | Stresses After Encapsulation                                                                                                                             |     |

|      | 8.6   | Finite Element Simulation                                                                                                                                |     |

|      | 8.7   | Stresses Due to Thermal Cycling and Moisture Absorption                                                                                                  |     |

|      | 8.8   | Summary                                                                                                                                                  |     |

| 9    |       | TRESS MEASUREMENTS IN 281 PIN CPGA PACKAGES                                                                                                              |     |

|      |       | G HIGH TEMPERATURE DIE ATTACHMENT MATERIALS                                                                                                              | 211 |

|      | 9.1   | Introduction                                                                                                                                             |     |

|      | 9.2   | 281 Pin CPGA Package Studies                                                                                                                             |     |

|      | 9.3   | Room Temperature Stresses                                                                                                                                |     |

|      | 9.4   | Stress Variation With Temperature                                                                                                                        |     |

|      | 9.5   | Aging and Thermal Cycling Reliability Tests                                                                                                              |     |

|      | 9.6   | Summary                                                                                                                                                  |     |

| 10   | SUMI  | MARY AND CONCLUSIONS                                                                                                                                     | 251 |

| BIBL | IOGRA | PHY                                                                                                                                                      | 255 |

| APPE | NDICE | S                                                                                                                                                        | 268 |

|      |       |                                                                                                                                                          |     |

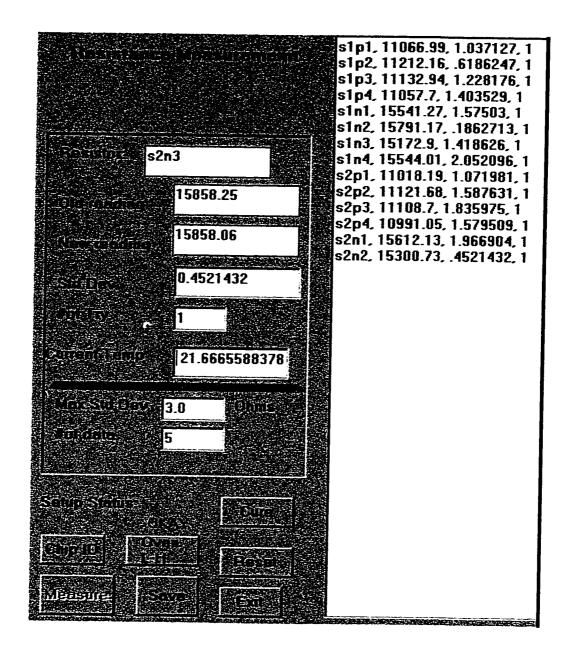

| Α | A VISUAL BASIC PROGRAM FOR GPIB CONTROLLED<br>RESISTANCE MEASUREMENTS OF BMW-2<br>SENSOR ROSETTES | 260 |

|---|---------------------------------------------------------------------------------------------------|-----|

|   | SENSOR ROSETTES                                                                                   | 269 |

| В | WIRING DIAGRAMS FOR AAA2, BMW-1, AND BMW-2                                                        |     |

|   | RESISTANCE MEASUREMENTS IN A CHIP CROSS                                                           |     |

|   | SECTION MANNER                                                                                    | 291 |

## LIST OF FIGURES

| 1.1  | Piezoresistive Sensor Concept                              | 3  |

|------|------------------------------------------------------------|----|

| 3.1  | Filamentary Silicon Conductor                              | 21 |

| 3.2  | (100) Silicon Wafer                                        | 25 |

| 3.3  | (111) Silicon Wafer                                        | 28 |

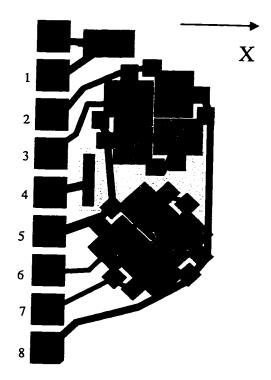

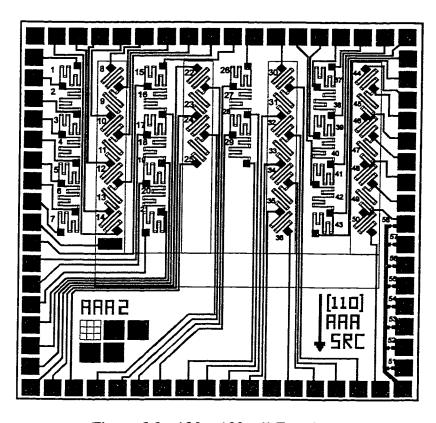

| 4.1  | AAA-2 (100) Silicon Test Chip                              | 32 |

| 4.2  | Optimized Measurement Rosette                              | 33 |

| 4.3  | Fabricated Measurement Rosette on AAA-2 Test Chip          | 36 |

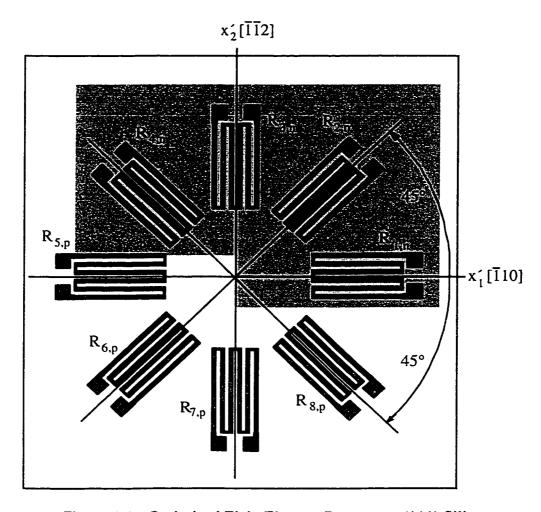

| 4.4  | Optimized Eight Element Rosette on (111) Silicon           | 37 |

| 4.5  | Calibration Methods to Obtain Piezoresistive Coefficients  | 43 |

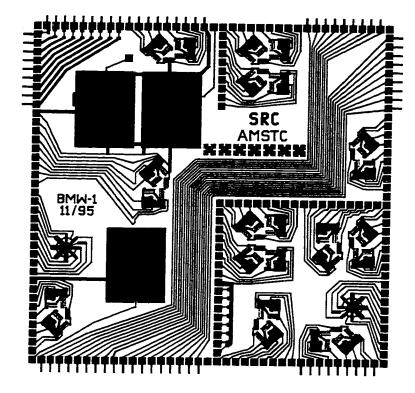

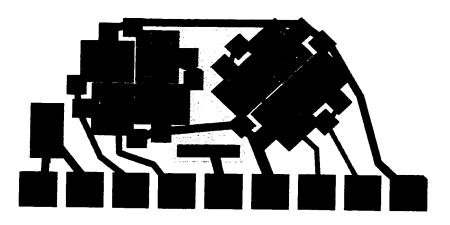

| 4.6  | BMW-1 Test Chip                                            | 44 |

| 4.7  | Fabricated Rosette on BMW-1 Test Chip                      | 44 |

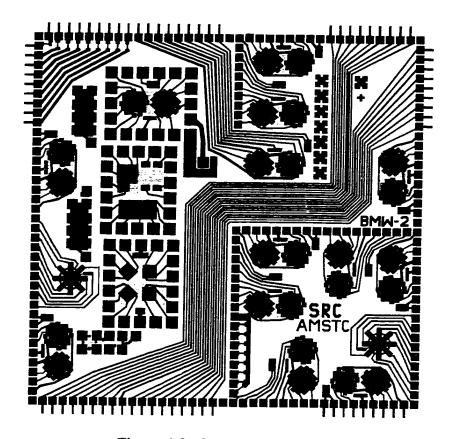

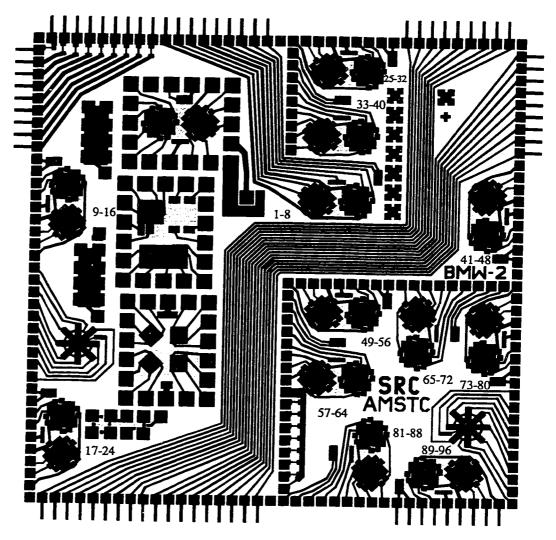

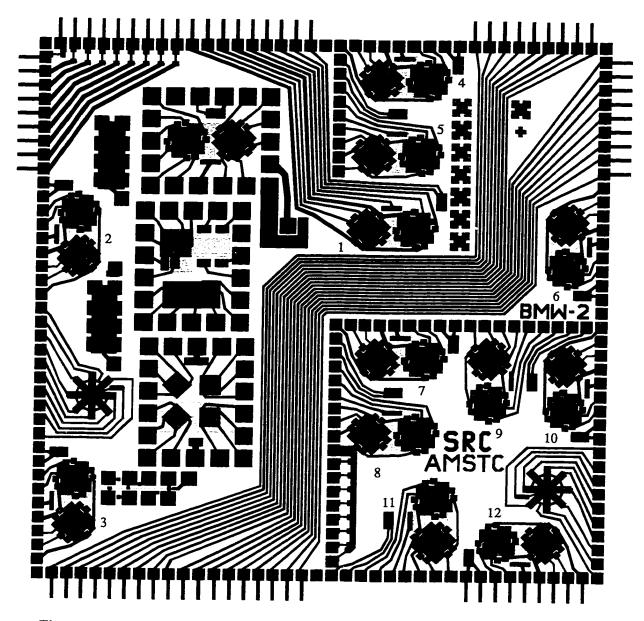

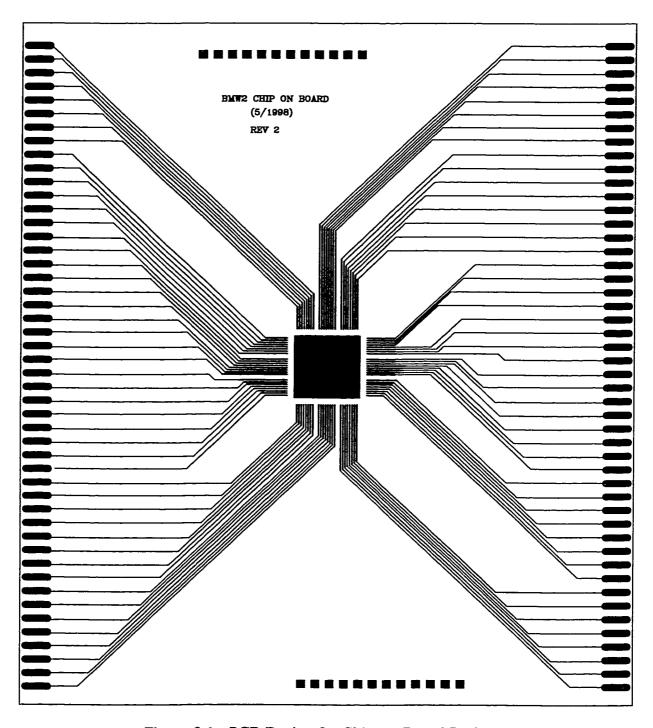

| 4.8  | BMW-2 Test Chip                                            | 47 |

| 4.9  | BMW-2 Sensor Rosette                                       | 47 |

| 4.10 | Cross Section Schematic of BMW-2 Resistors                 | 48 |

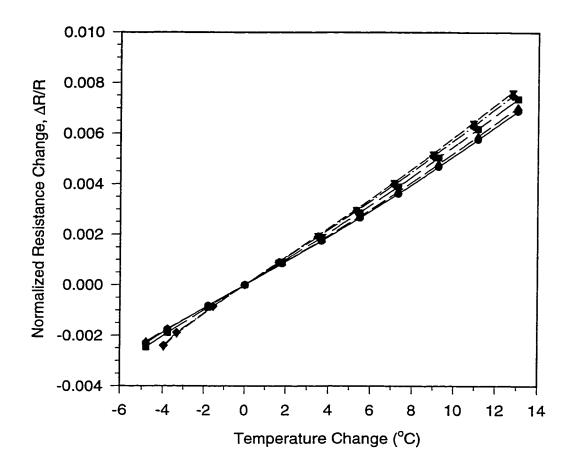

| 4.11 | Variation of Normalized Resistance Change with Temperature | 52 |

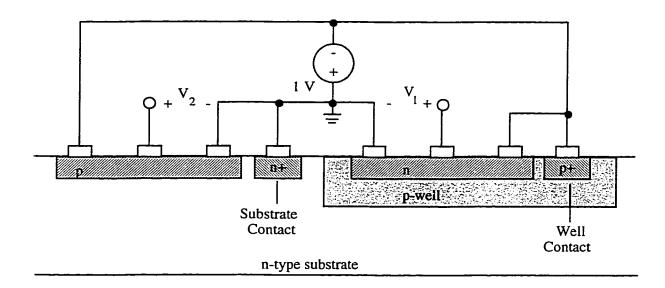

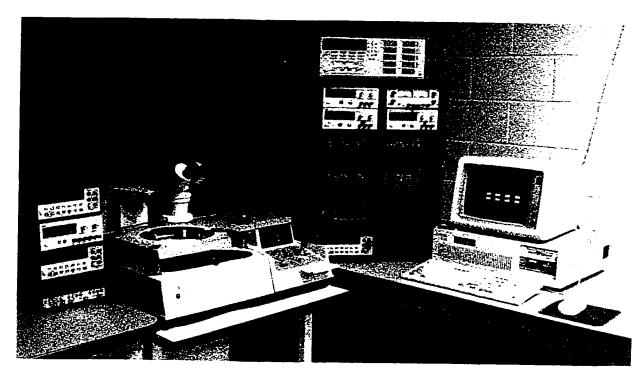

| 4.12 | Experimental Setup for Test Chip Characterization          | 57 |

| 4.13 | Basic BMW-2 Test Chip with Resistor Numbering              | 58 |

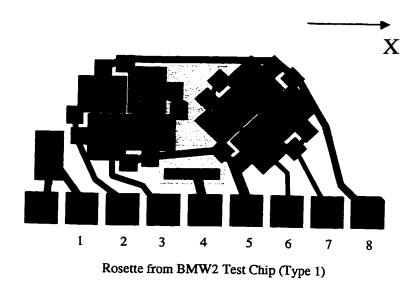

| 1.14 | Two Types of Rosette from BMW-2 Test Chip                  | 65 |

| 4.15 | Measurement rosette Numbering 200 x 200 mil BMW-2 Test Chip                                                        | 66 |

|------|--------------------------------------------------------------------------------------------------------------------|----|

| 4.16 | Typical Resistance Measurement Wiring Diagram for the BMW-2                                                        |    |

|      | Test Chip Rosette                                                                                                  | 67 |

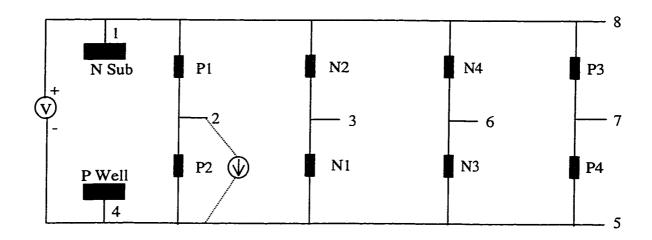

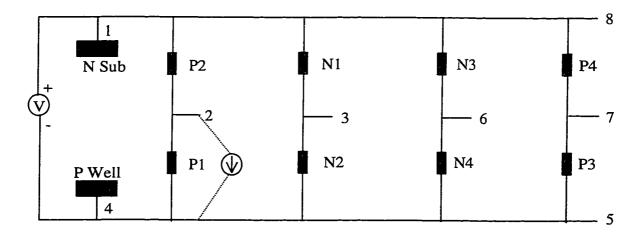

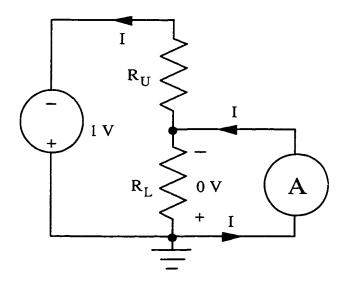

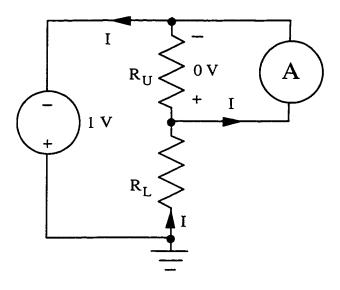

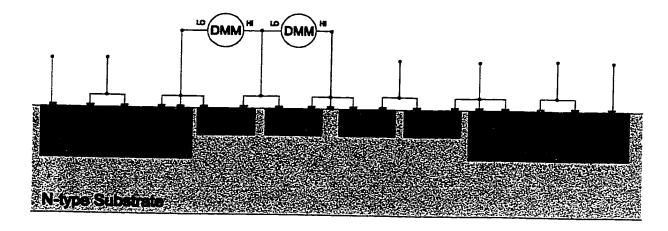

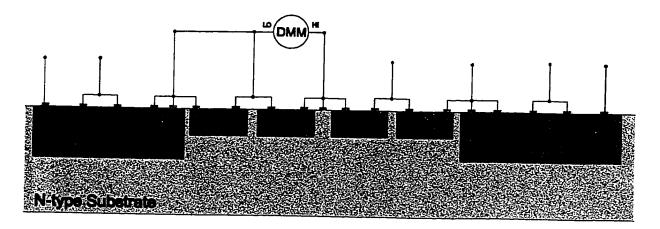

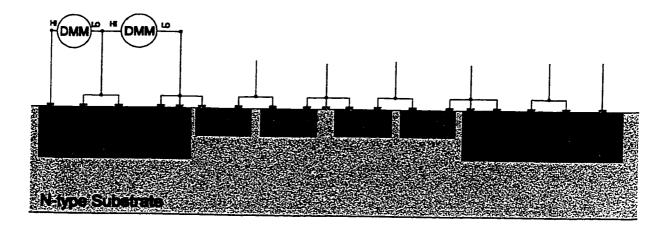

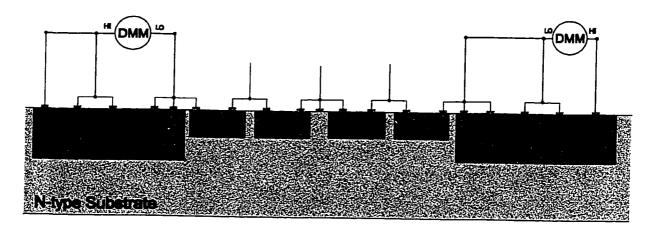

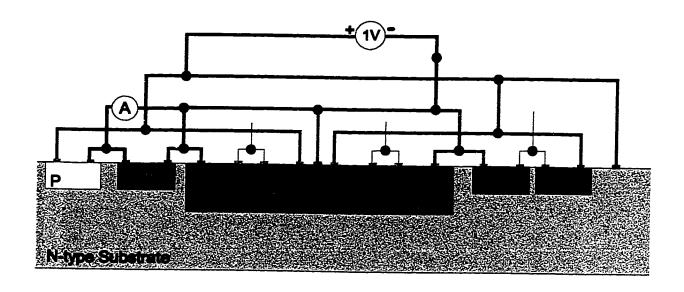

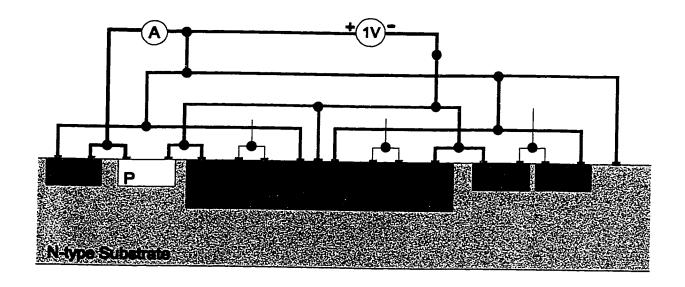

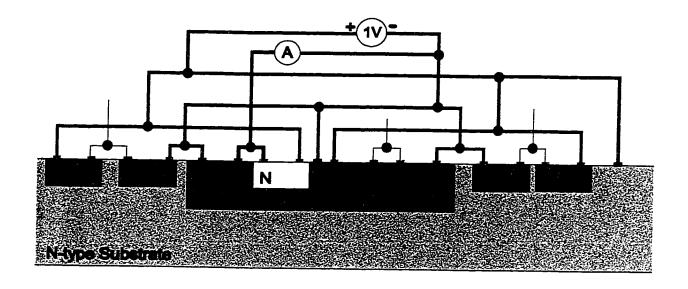

| 4.17 | Bias for Resistance Measurements of BMW-2 Sensor Rosette                                                           | 70 |

| 4.18 | Bias for Resistance Measurements                                                                                   | 70 |

| 4.19 | Bias for Resistance Measurements                                                                                   | 71 |

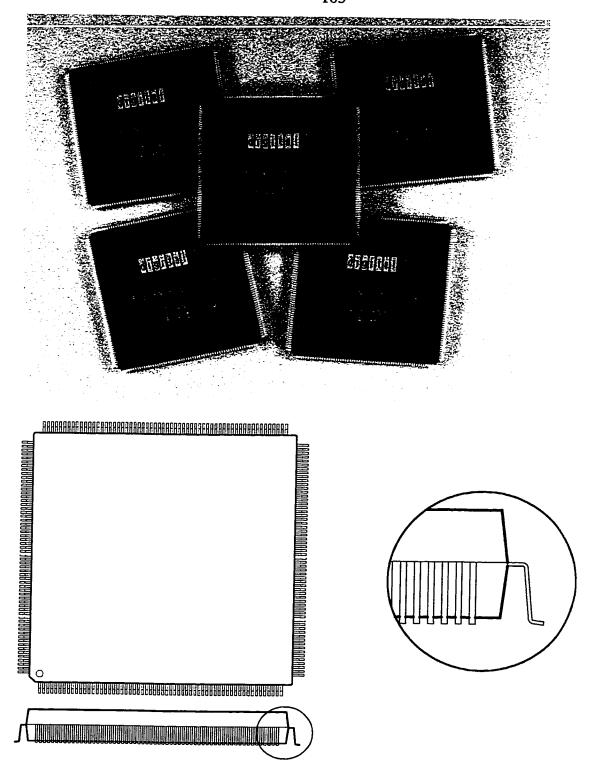

| 5.1  | PLCC Package and Lead Frame Strip with Test Die                                                                    | 74 |

| 5.2  | 100 x 100 mil Test Chip                                                                                            | 75 |

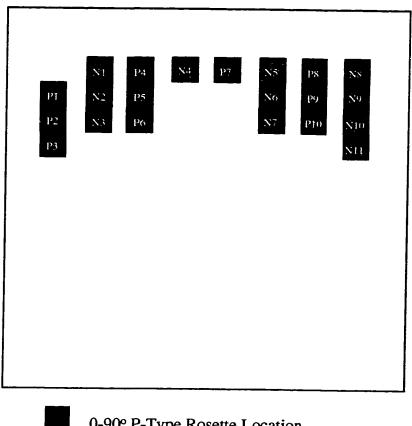

| 5.3  | Sensor Rosette Locations (44 Pin PLCC)                                                                             | 77 |

| 5.4  | Finite Element Mesh (One Quarter near the Die)                                                                     |    |

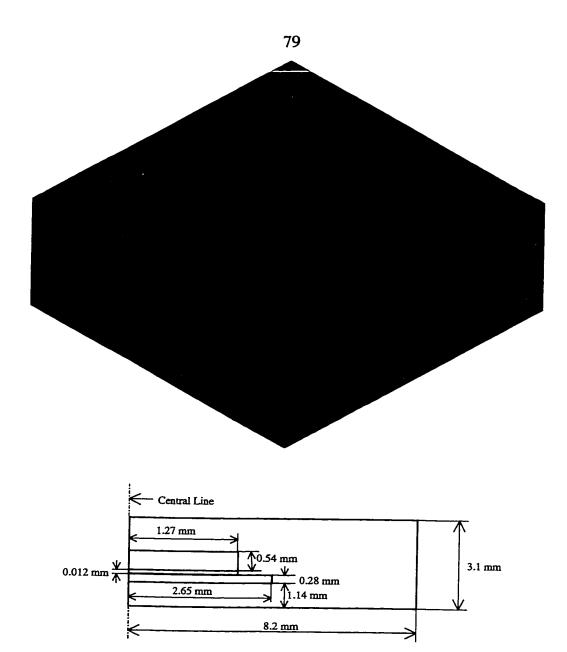

|      | and Model Dimensions (44 Pin PLCC)                                                                                 | 79 |

| 5.5  | In-Plane Shear Stress Distribution Finite Element Contours and Experimental Data (44 Pin PLCC)                     | 80 |

| 5.6  | In-Plane Normal Stress Difference Distribution Finite Element Contours and Experimental Data (44 Pin PLCC)         | 81 |

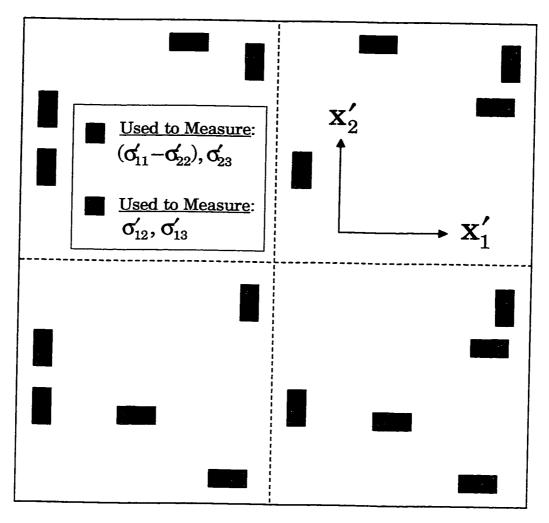

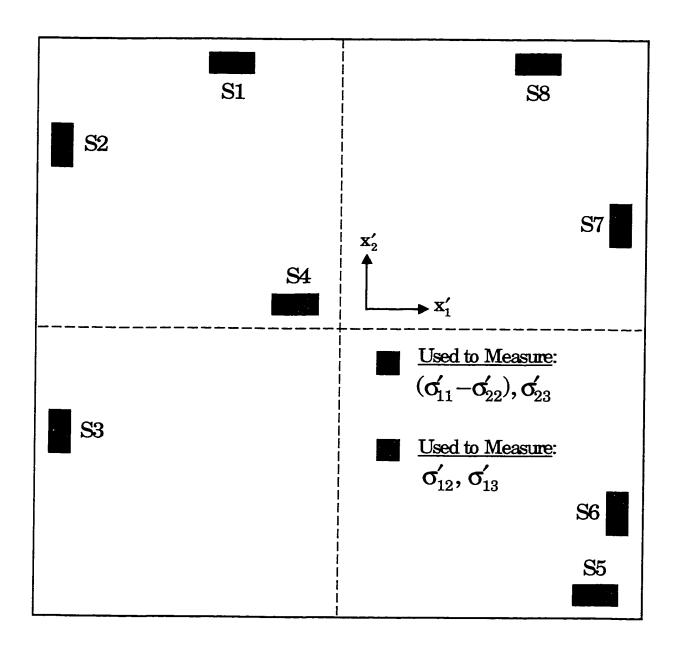

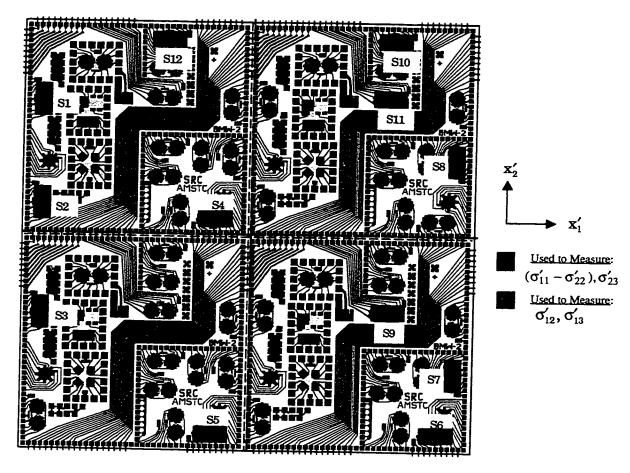

| 5.7  | Sensor Rosette Locations (400 x 400 mil Test Chip), 160 Pin QFP                                                    | 83 |

| 5.8  | PCB Design for Package Socket, 160 Pin QFP                                                                         | 85 |

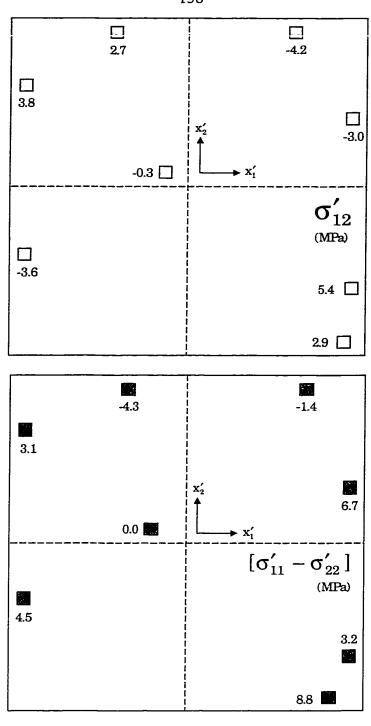

| 5.9  | Die Stresses After Encapsulation, 160 Pin QFP                                                                      | 86 |

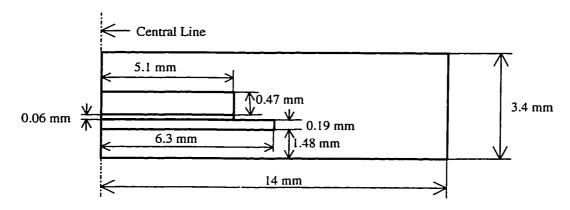

| 5.10 | Cross Section of a half 160 QFP for FEM Simulation                                                                 | 90 |

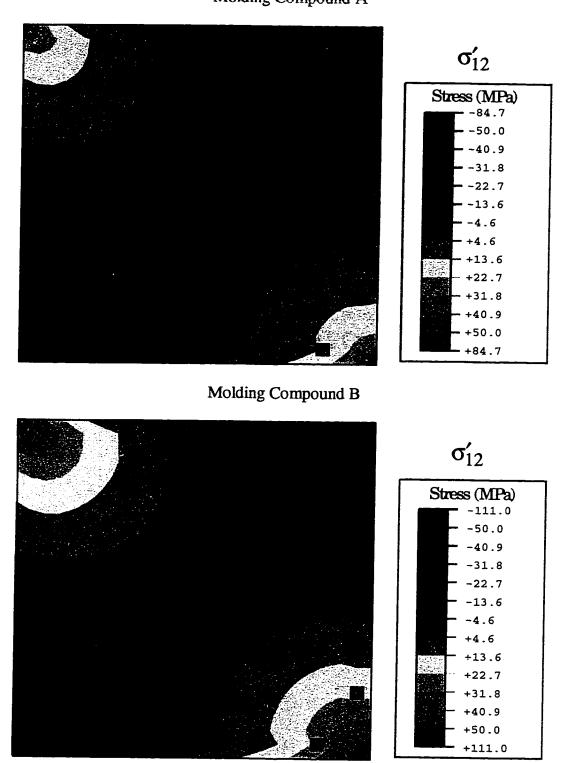

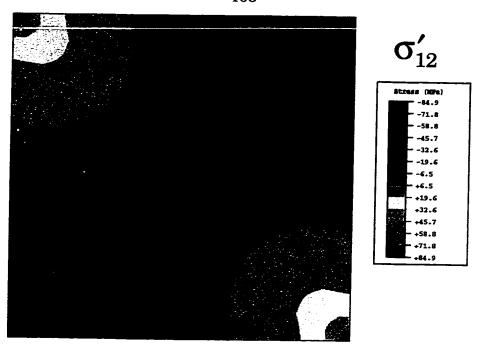

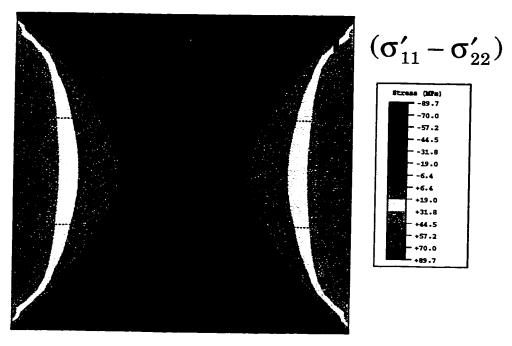

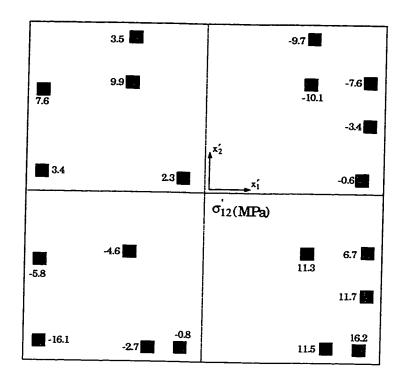

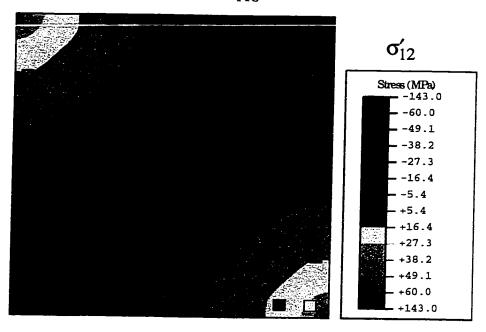

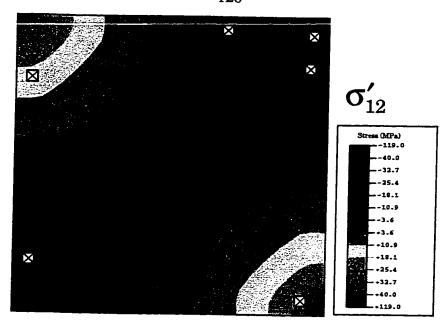

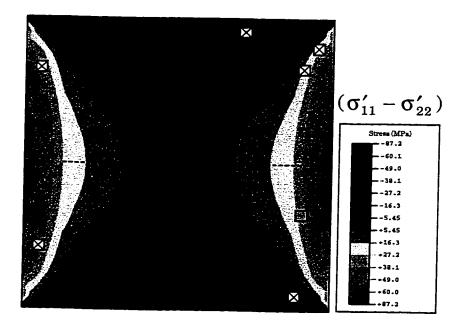

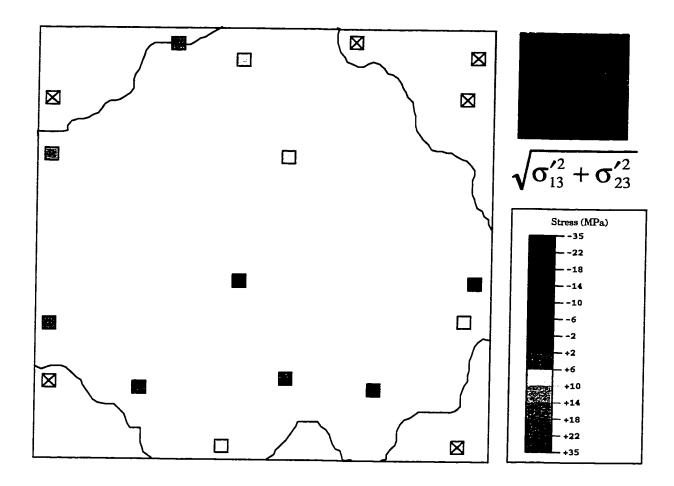

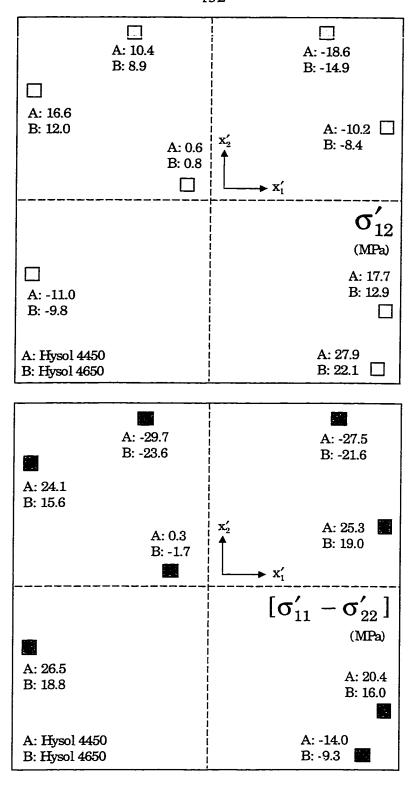

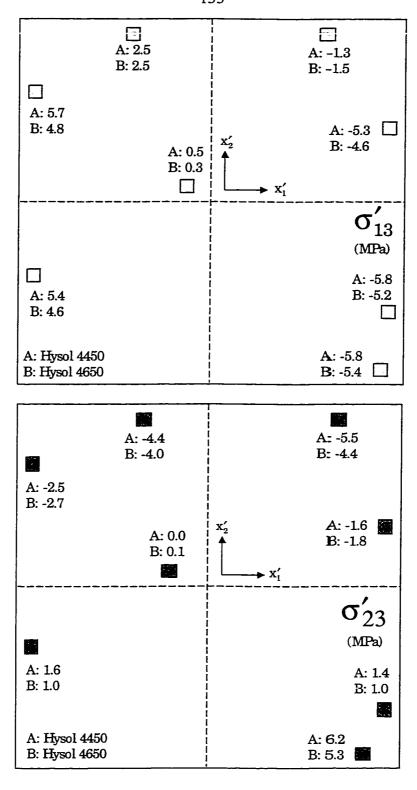

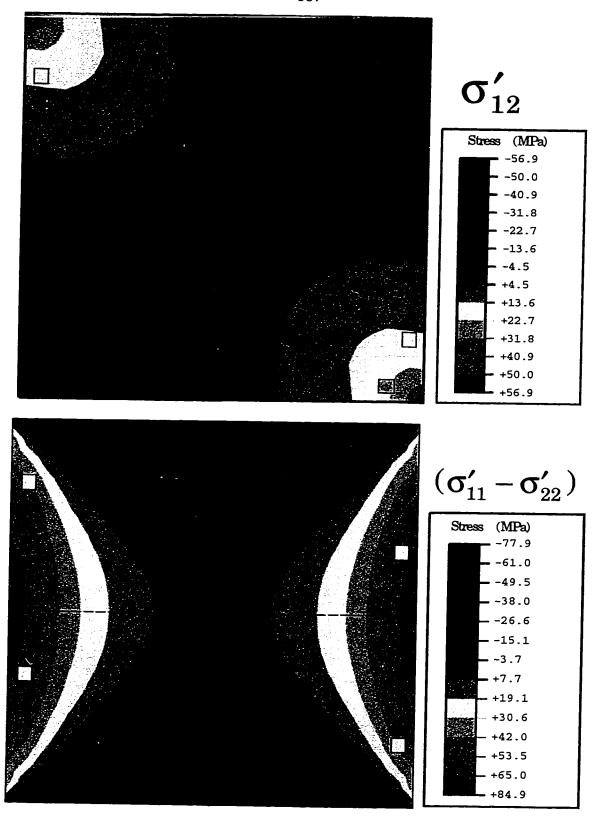

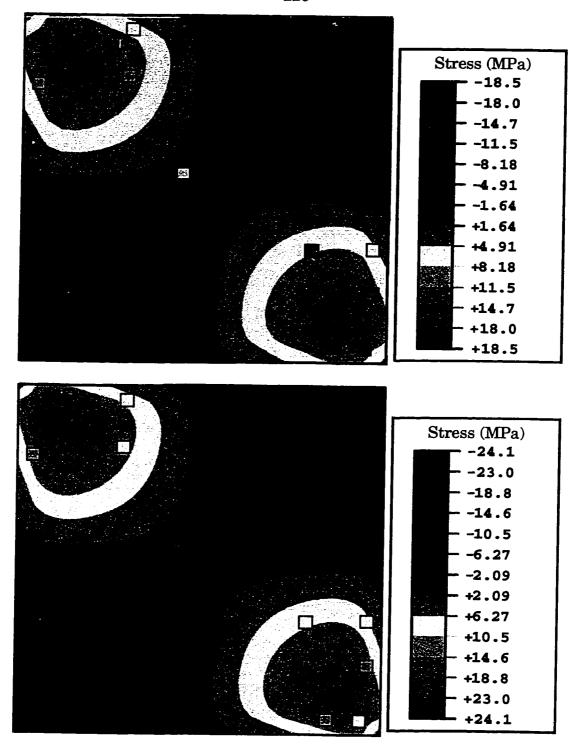

| 5.11 | In-Plane Shear Stress Distribution Finite Element Contours and Experimental Data (160 Pin QFP)                     | 91 |

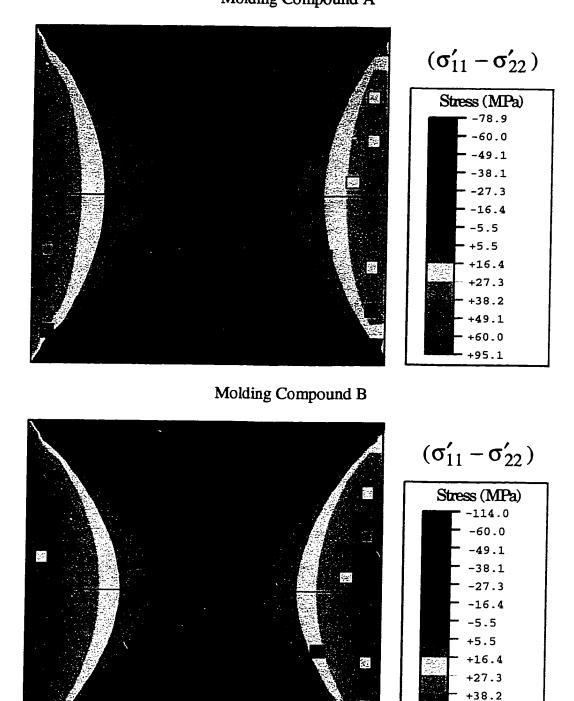

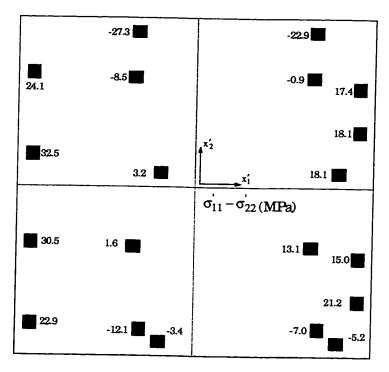

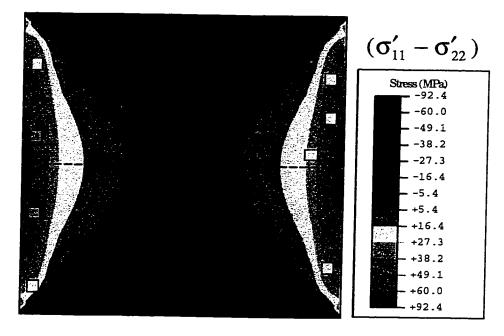

| 5.12 | In-Plane Normal Stress Difference Distribution Finite Element Contours and Experimental Data (160 Pin QFP)         | 92 |

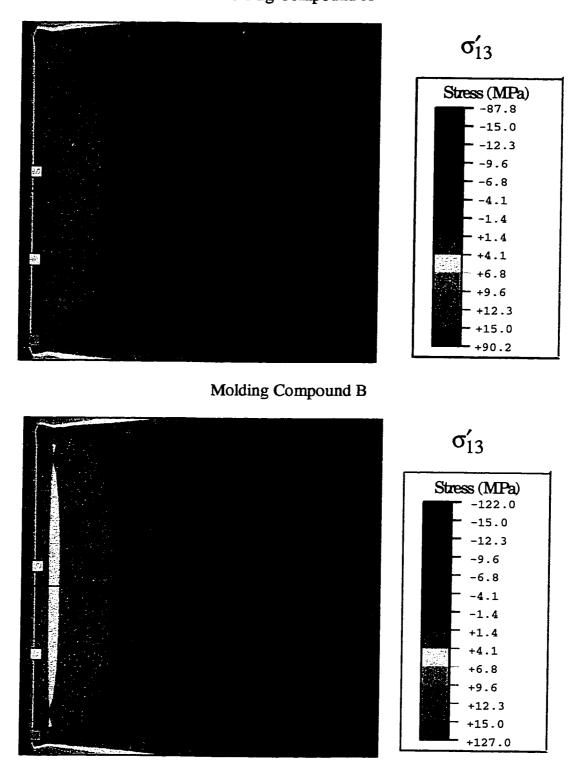

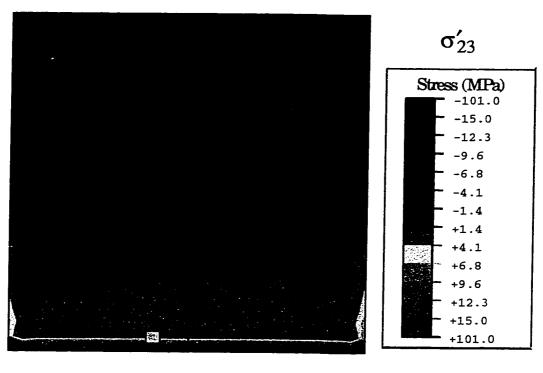

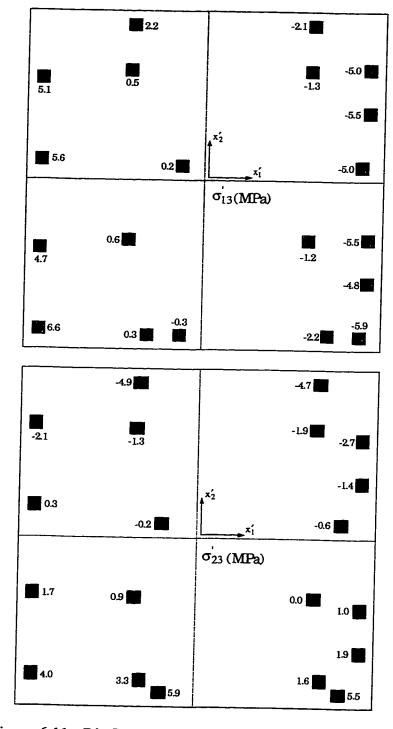

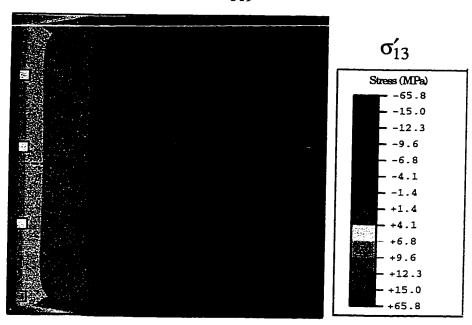

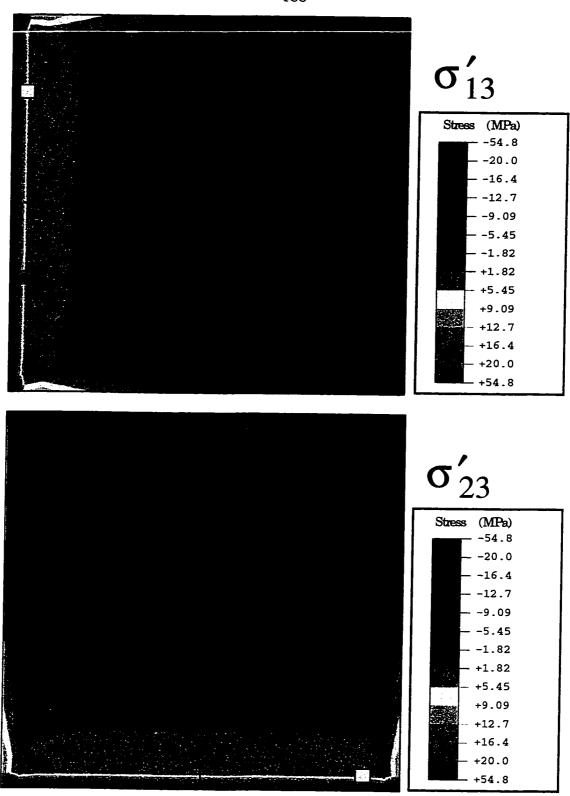

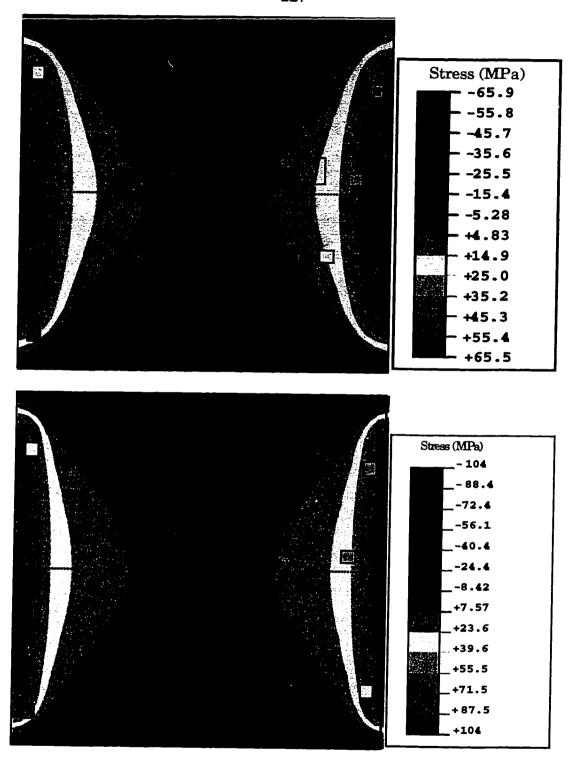

| 5.13 | Out-of-Plane Shear Stress $\sigma'_{13}$ Distribution  Finite Element Contours and Experimental Data (160 Pin OFP) | 02 |

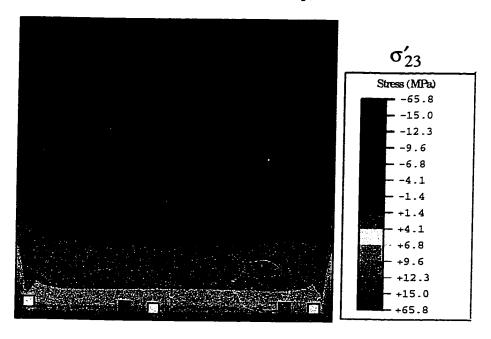

| 5.14 | Out-of-Plane Shear Stress $\sigma_{23}$ Distribution<br>Finite Element Contours and Experimental Data(160 Pin QFP) | 94  |

|------|--------------------------------------------------------------------------------------------------------------------|-----|

| 6.1  | AAA2 Test Chip Attached to Lead Frame                                                                              | 100 |

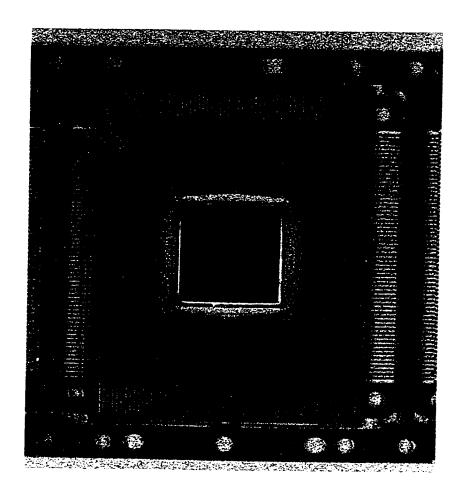

| 6.2  | Encapsulated Test Chip in Measurement Socket                                                                       | 102 |

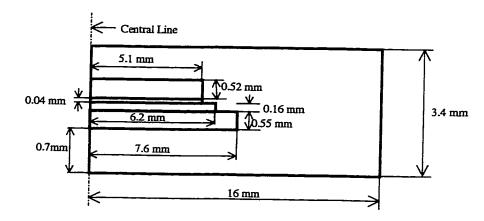

| 6.3  | Schematic of Packaged Die (240 Pin QFP)                                                                            | 103 |

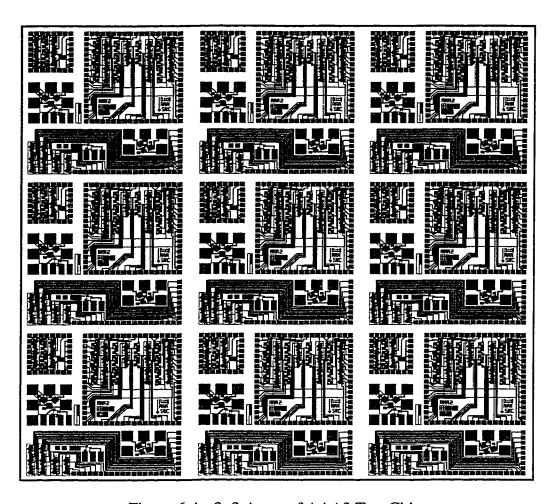

| 6.4  | 3 x 3 Array of AAA2 Test Chip                                                                                      | 104 |

| 6.5  | AAA2 Sensor Rosette Locations (450 x 450 mil Test Chip)                                                            | 105 |

| 6.6  | Finite Element Mesh for the 240 pin QFP (One Quarter Model near the Die)                                           | 107 |

| 6.7  | In-Plane Shear Stress Distribution Finite Element Contours and Experimental Data                                   | 108 |

| 6.8  | In-Plane Normal Stress Difference Distribution Finite Element Contours and Experimental Data                       | 108 |

| 6.9  | BMW-2 Sensor Rosette Locations (400 x 400 mil Test Chip)                                                           | 110 |

| 6.10 | Wiring Diagram of Wire Bonding                                                                                     | 111 |

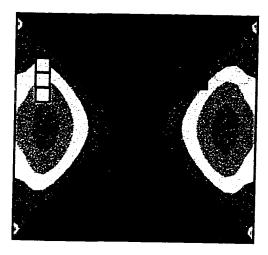

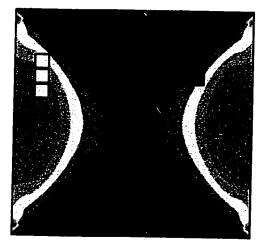

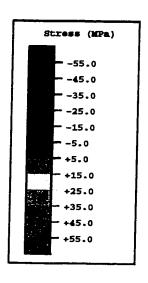

| 6.11 | Die Stresses after Encapsulation                                                                                   | 113 |

| 6.12 | Cross-Sectional Dimensions for the 240 Pin QFP                                                                     | 117 |

| 6.13 | FEM Mesh for the 240 Pin QFP (One Quarter Model near the Die)                                                      | 117 |

| 6.14 | In-Plane Shear Stress Distribution Finite Element Contours and Experimental Data                                   | 118 |

| 6.15 | In-Plane Normal Stress Difference Distribution Finite Element Contours and Experimental Data                       | 118 |

| 6.16 | Out-of-Plane Shear Stress $\sigma'_{13}$ Distribution<br>Finite Element Contours and Experimental Data             | 119 |

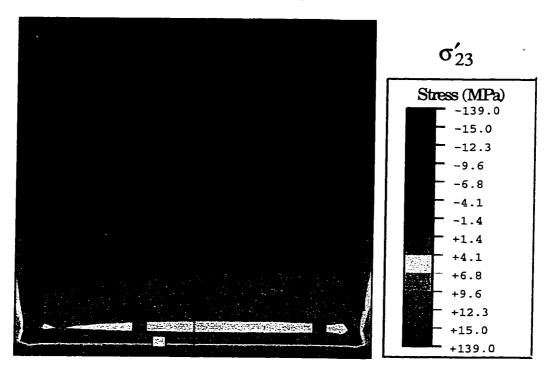

| 5.17 | Out-of-Plane Shear Stress $\sigma'_{23}$ Distribution<br>Finite Element Contours and Experimental Data             | 119 |

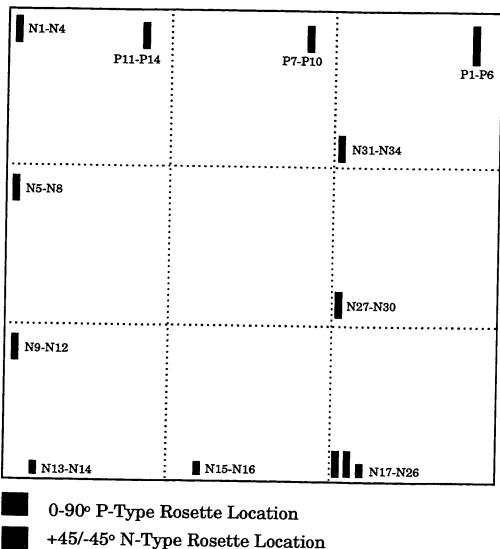

| 6.18 | BMW-1 Sensor Rosette Locations (400 x 400 mil Test Chip)                                                                  | 121 |

|------|---------------------------------------------------------------------------------------------------------------------------|-----|

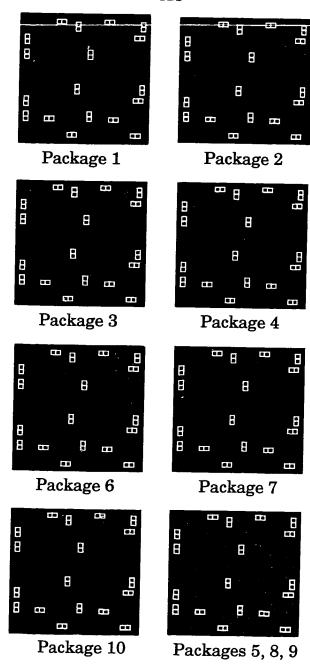

| 6.19 | C-SAM Images of the Encapsulated BMW-1 Test Chips                                                                         | 123 |

| 6.20 | In-Plane Shear Stress Distribution Finite Element Contours and Experimental Data                                          | 126 |

| 6.21 | In-Plane Normal Stress Difference Distribution Finite Element Contours and Experimental Data                              | 126 |

| 6.22 | Total Out-of-Plane Shear Stress Data for a Typical Delaminated Die (Package # 1)                                          | 128 |

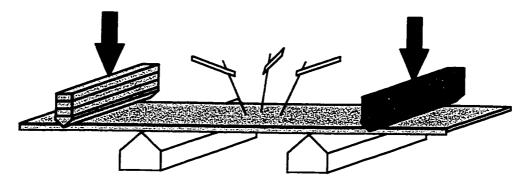

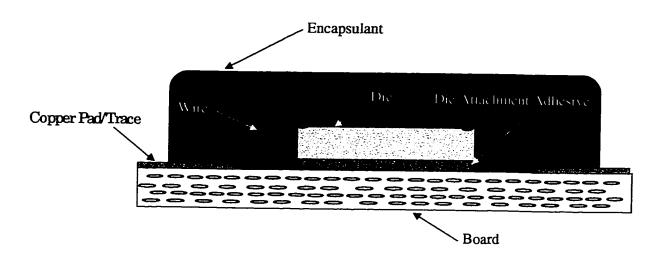

| 7.1  | Wire Bonded COB                                                                                                           | 132 |

| 7.2  | Chip-on-Board Specimen with Encapsulated Test Chip                                                                        | 135 |

| 7.3  | Sensor Rosette Locations (400 x 400 mil Test Chip, COB)                                                                   | 136 |

| 7.4  | Measured Stresses Caused by Die Attachment (COB)                                                                          | 138 |

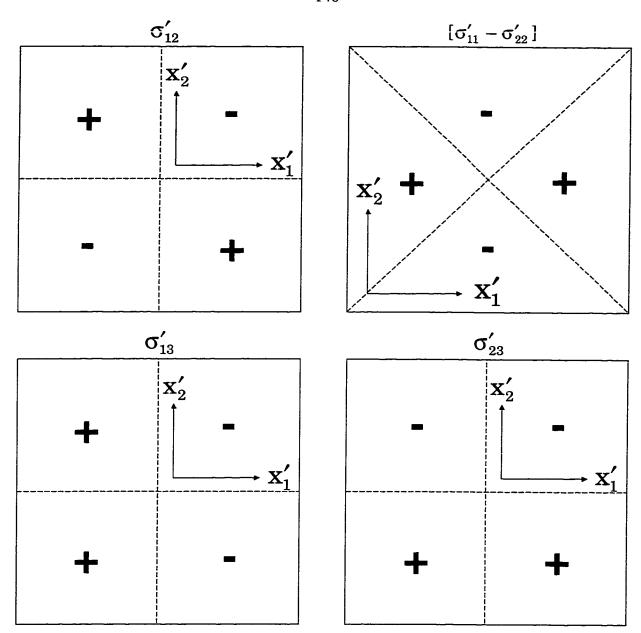

| 7.5  | Signs of Idealized Encapsulated Die Stress Distribution                                                                   | 140 |

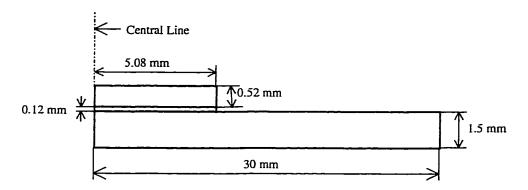

| 7.6  | Dimensions of COB Die Attachment Model                                                                                    | 143 |

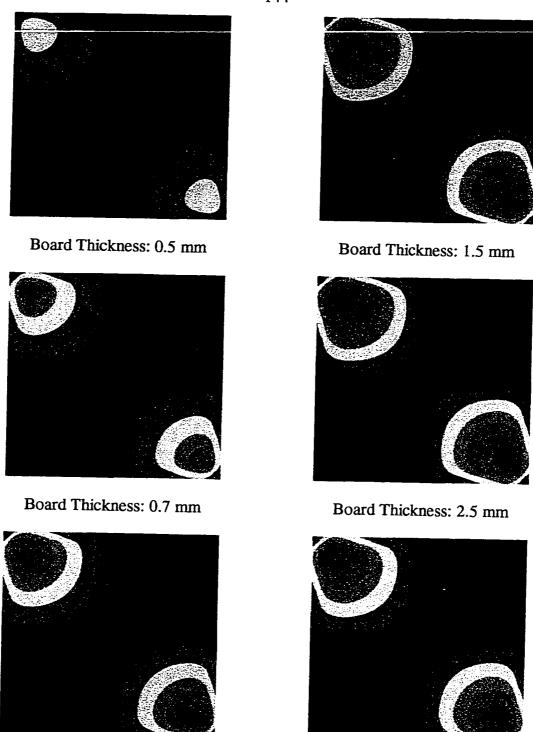

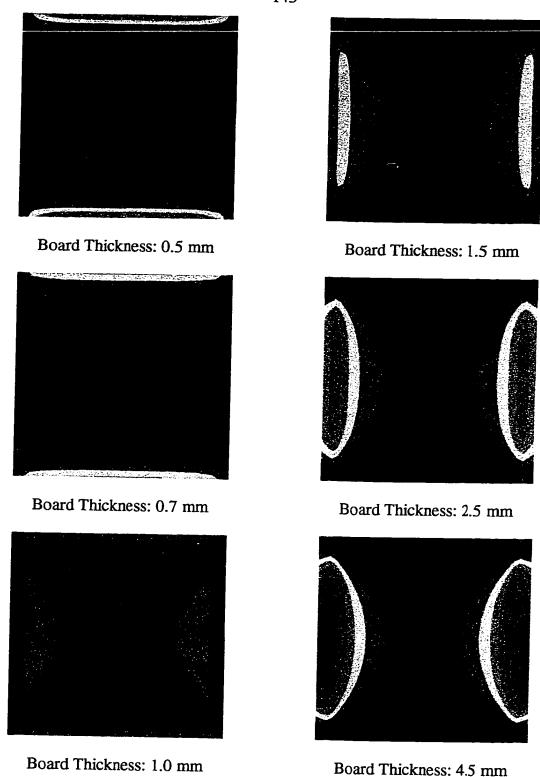

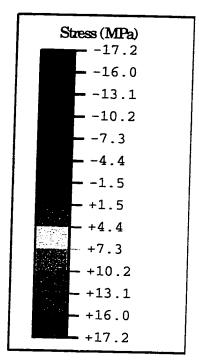

| 7.7  | Die Surface Stress Distribution with Varying Board Thickness                                                              | 144 |

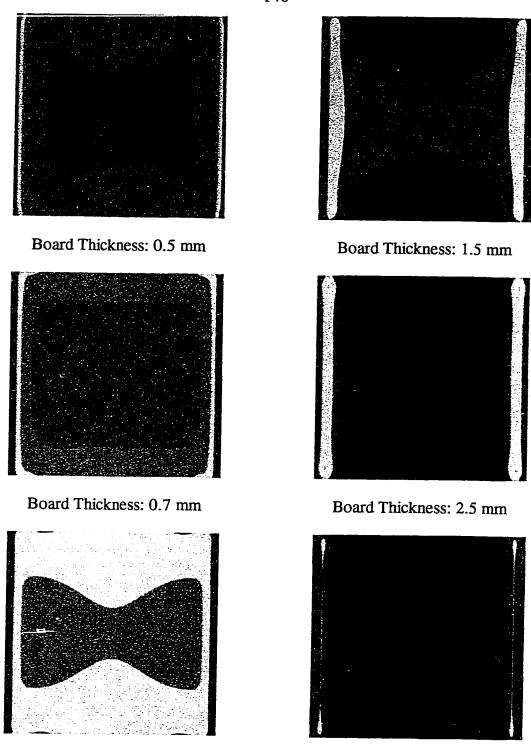

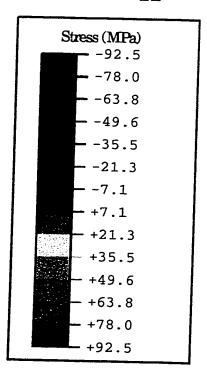

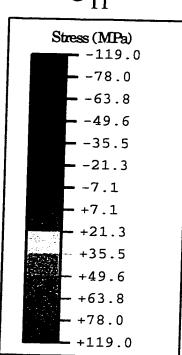

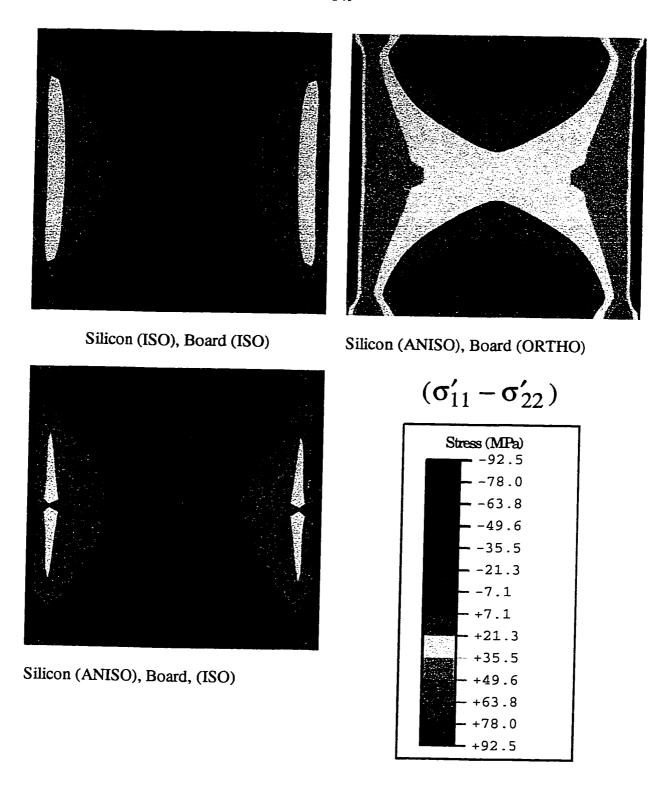

| 7.8  | Die Surface Stress Distribution with Varying Material Properties (ISO: Isotropic, ANISO: Anisotropic, ORTHO: Orthotropic) | 149 |

| 7.9  | Variation of Die Attachment Stress with Temperature (COB)                                                                 | 151 |

| 7.10 | Comparison of Measured Stresses after Encapsulation for Two Encapsulants (COB)                                            | 152 |

| 7.11 | Variation of Encapsulation Stress with Temperature (COB)                                                                  | 156 |

| 7.12 | Stress Variation During Encapsulant Cure (COB)                                                                            | 159 |

| 7.13 | Stress Variation During Encapsulant Cure (COB)                                                                            | 162 |

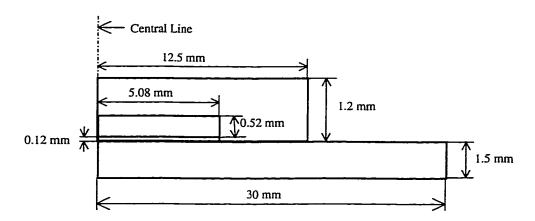

| 7.14 | COB Finite Element Mesh (One Quarter Model Near the Die)                                                                  | 164 |

| 7.15 | Dimensions of COB Encapsulation Model                                                                                     | 165 |

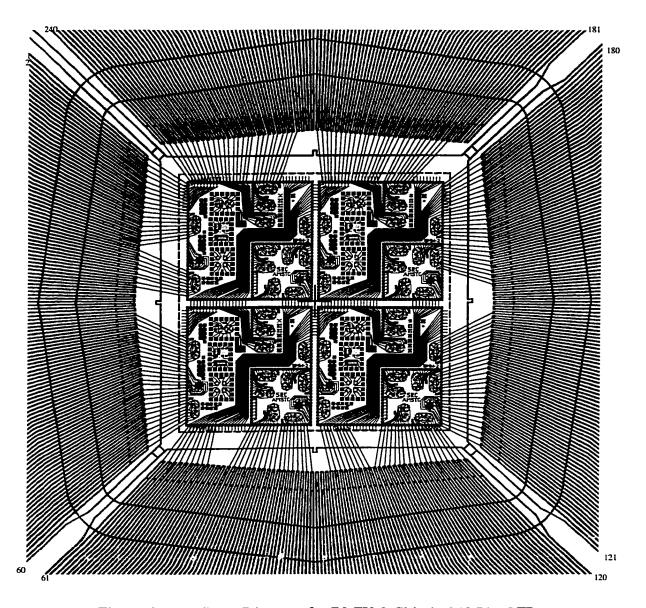

| 7.16 | Finite Element Contours and Experimental Data (COB)                                           | 167 |

|------|-----------------------------------------------------------------------------------------------|-----|

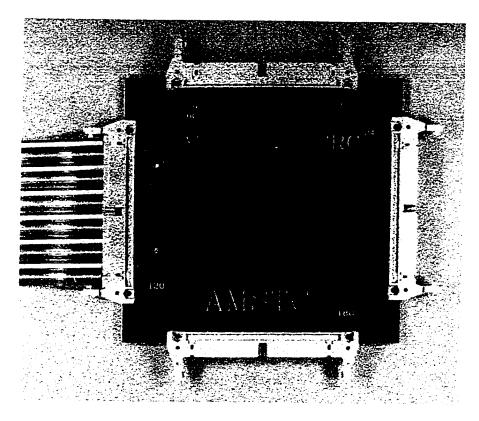

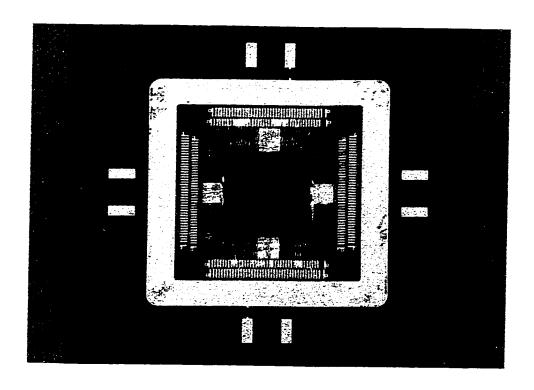

| 8.1  | PCB Design for Chip-on-Board Package                                                          | 174 |

| 8.2  | Sensor Rosette Locations (400 x 400 mil Chip) (COB Study #2)                                  | 175 |

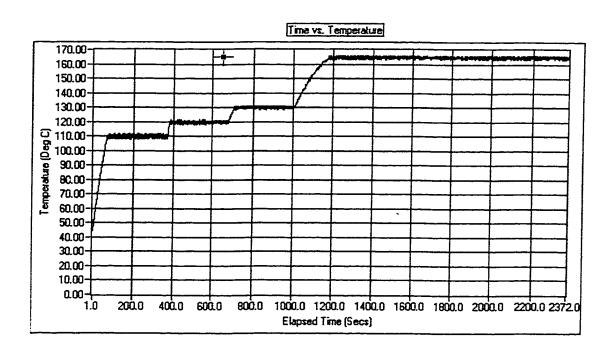

| 8.3  | VFM Curing Profile                                                                            | 177 |

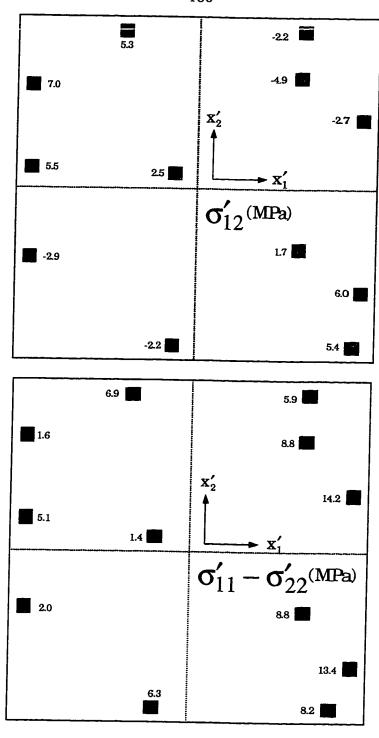

| 8.4  | Measured Stresses after Die Attachment                                                        | 180 |

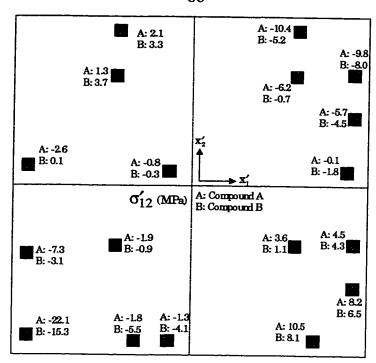

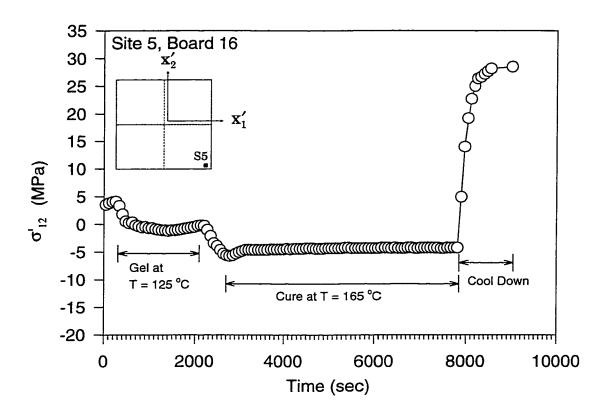

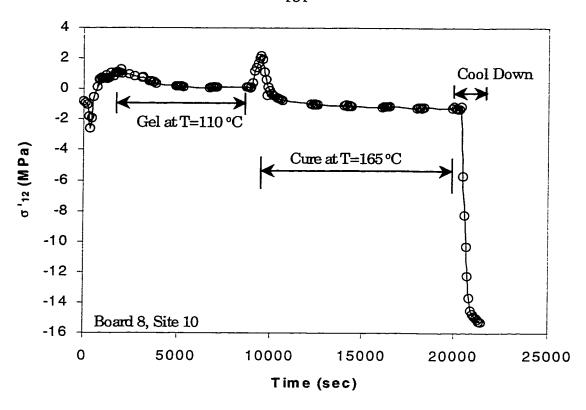

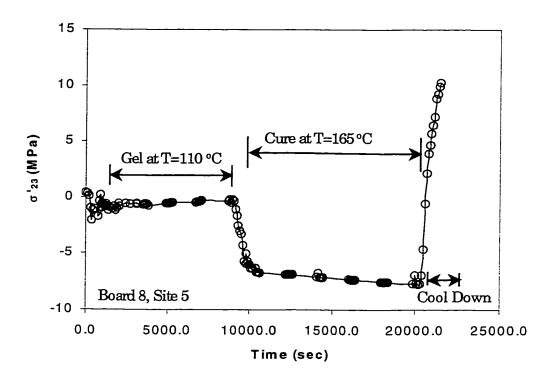

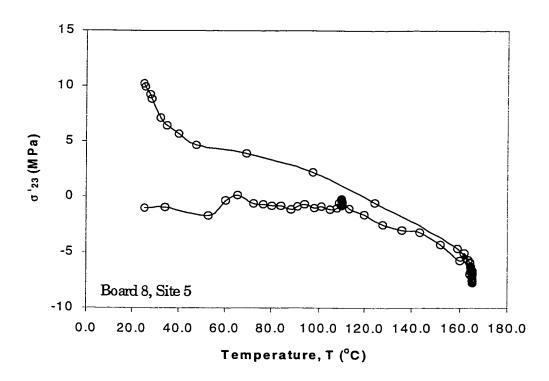

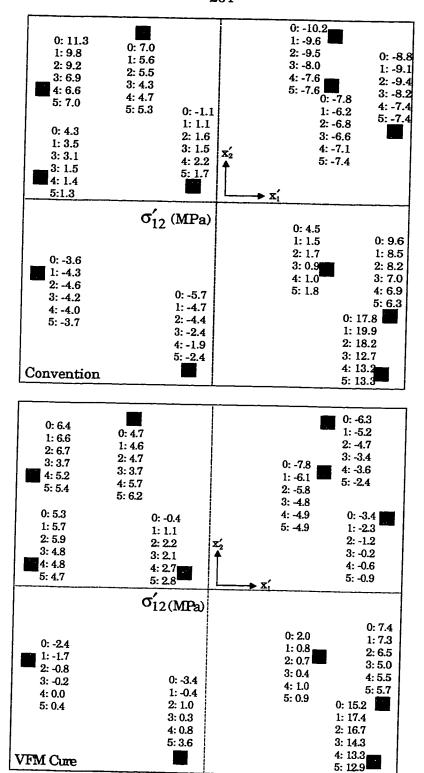

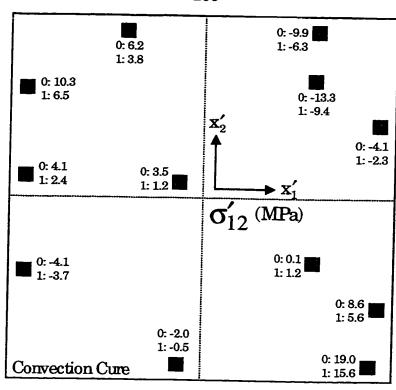

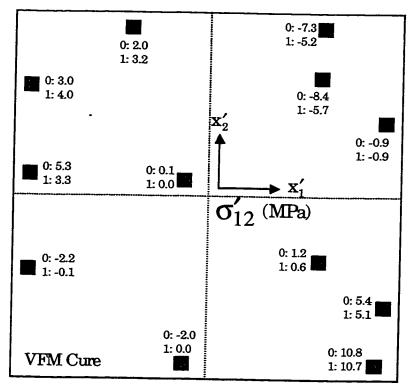

| 8.5  | Stress Variation During Convection Cure $(\sigma'_{12})$                                      | 181 |

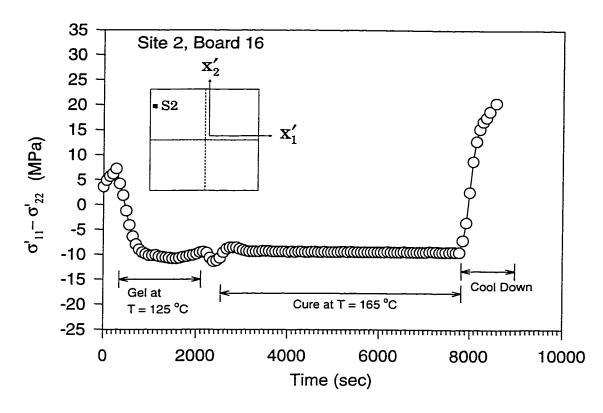

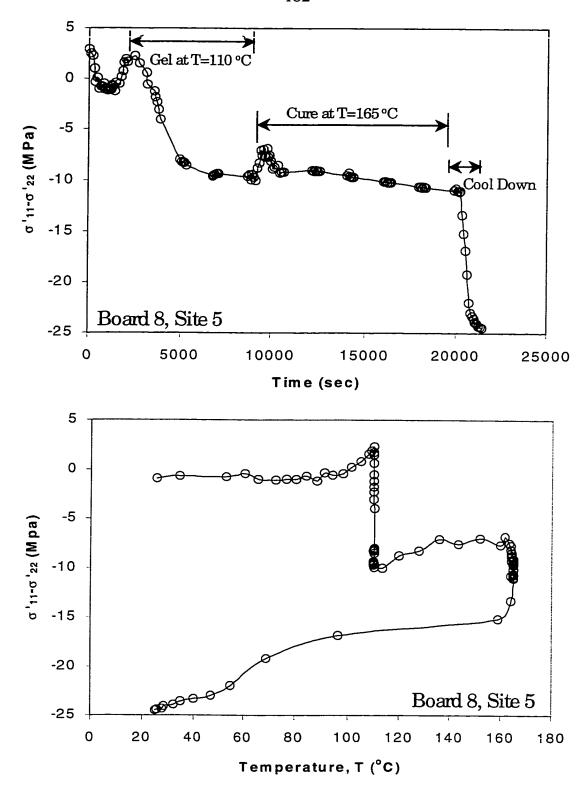

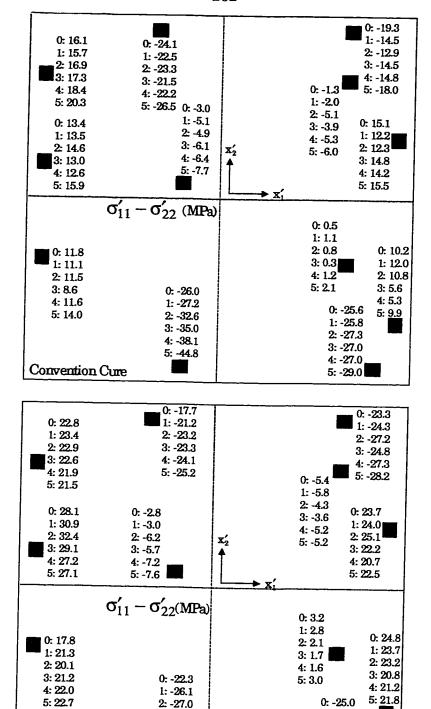

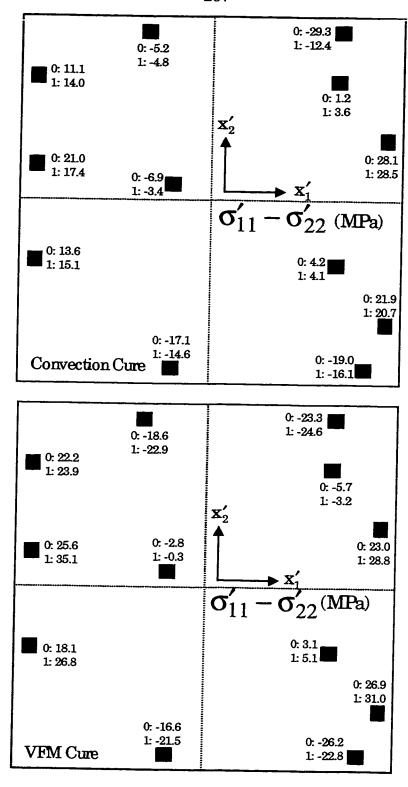

| 8.6  | Stress Variation During Convection Cure $(\sigma'_{11} - \sigma'_{22})$                       | 182 |

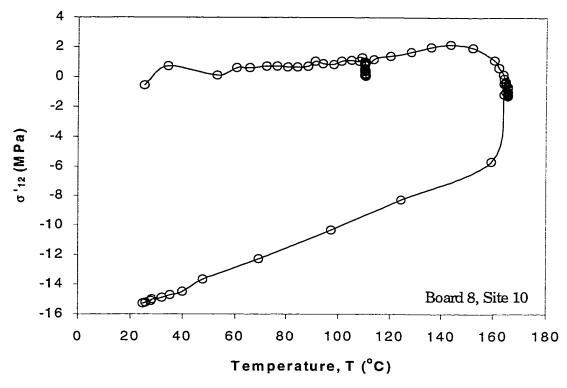

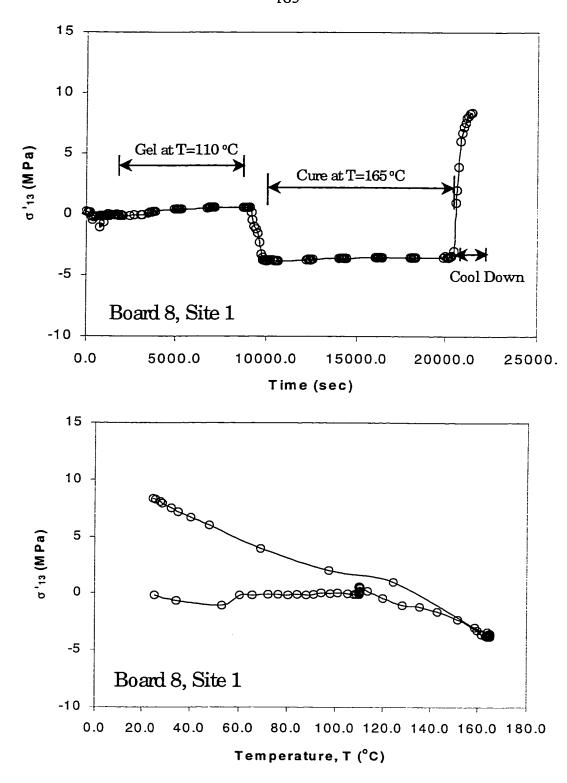

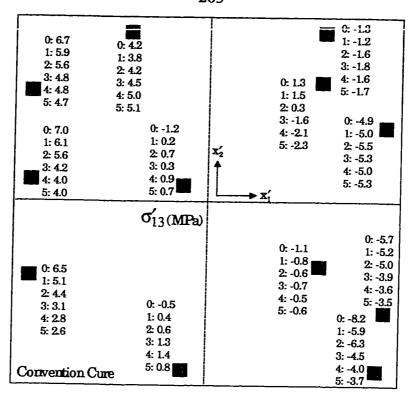

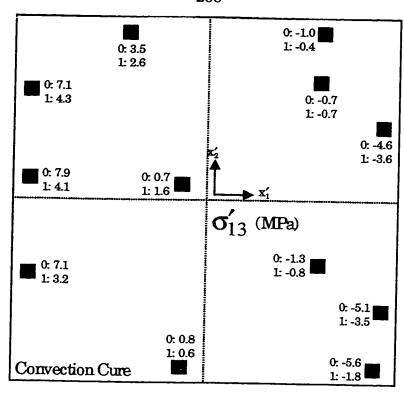

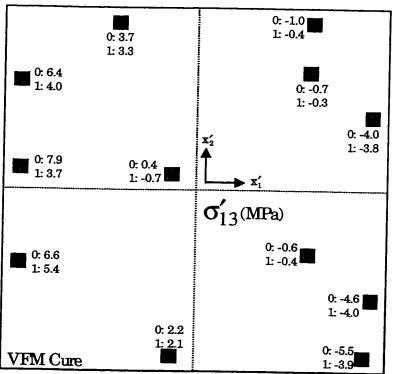

| 8.7  | Stress Variation During Convection Cure ( $\sigma'_{13}$ )                                    | 183 |

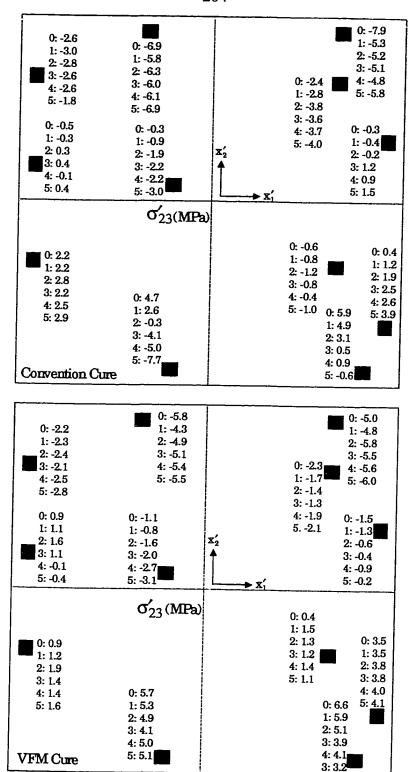

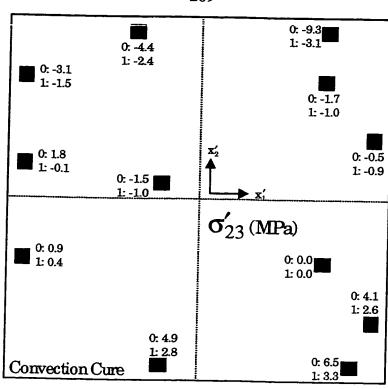

| 8.8  | Stress Variation During Convection Cure ( $\sigma'_{23}$ )                                    | 184 |

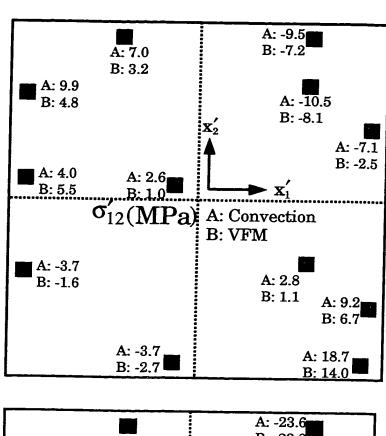

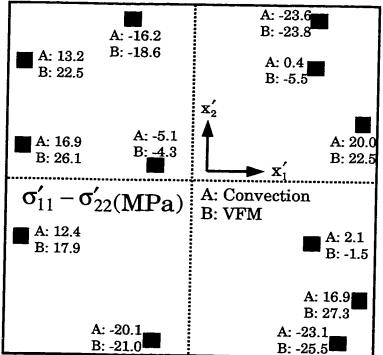

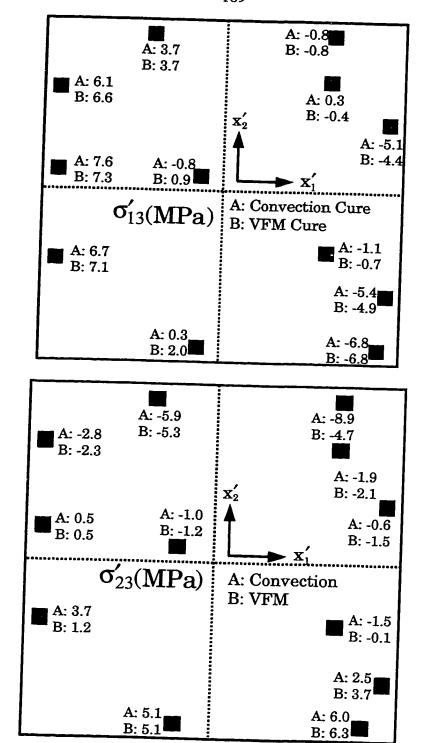

| 8.9  | Die Stresses after Encapsulation                                                              | 188 |

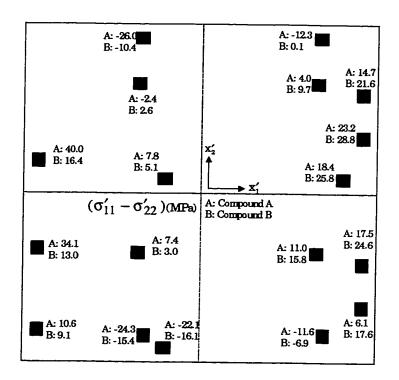

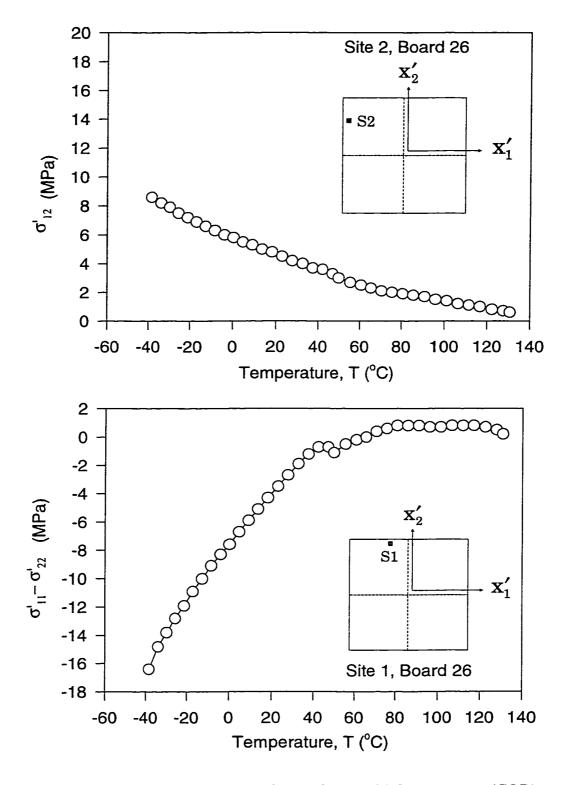

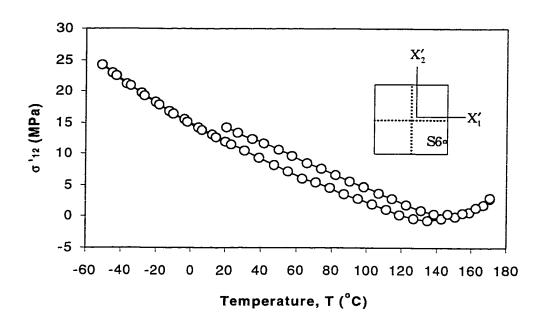

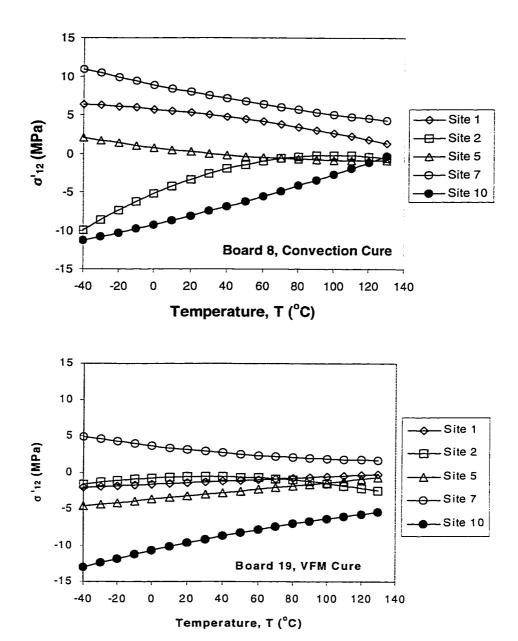

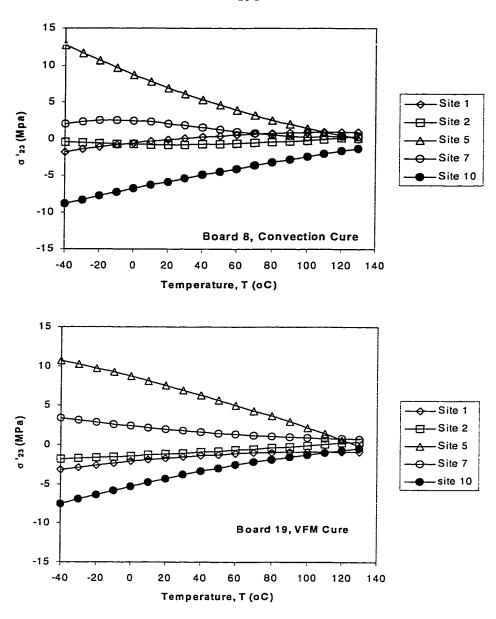

| 8.10 | Variation of Final Packaged Die Stress with Temperature ( $\sigma'_{12}$ )                    | 190 |

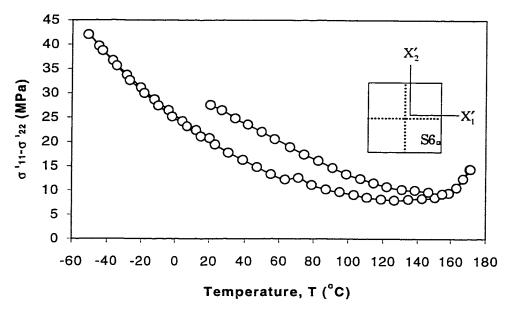

| 8.11 | Variation of Final Packaged Die Stress with Temperature ( $\sigma'_{11} - \sigma'_{22}$ )     | 191 |

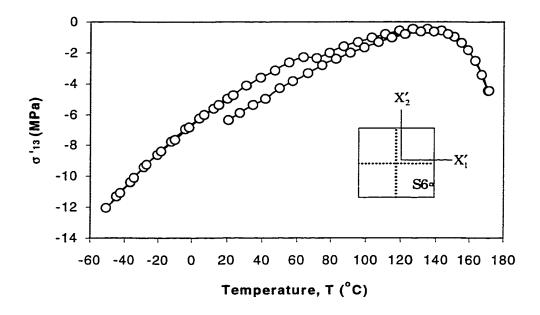

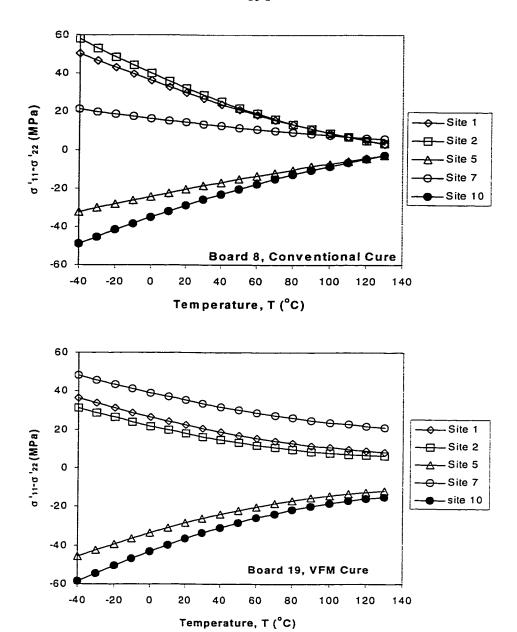

| 8.12 | Variation of Final Packaged Die Stress with Temperature ( $\sigma'_{13}$ )                    | 192 |

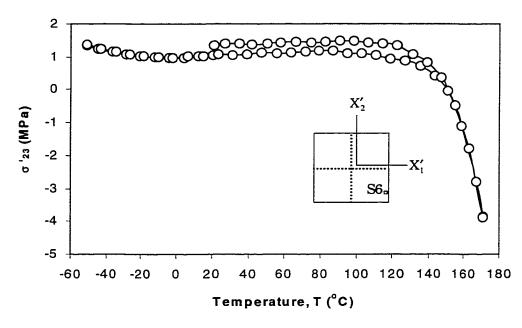

| 8.13 | Variation of Final Packaged Die Stress with Temperature ( $\sigma'_{23}$ )                    | 193 |

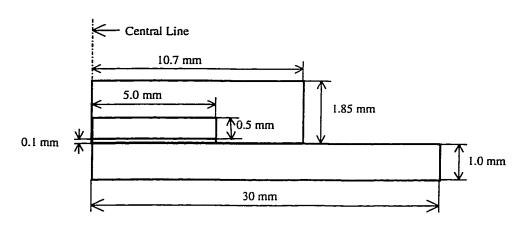

| 8.14 | Dimensions of COB Encapsulation Model                                                         | 196 |

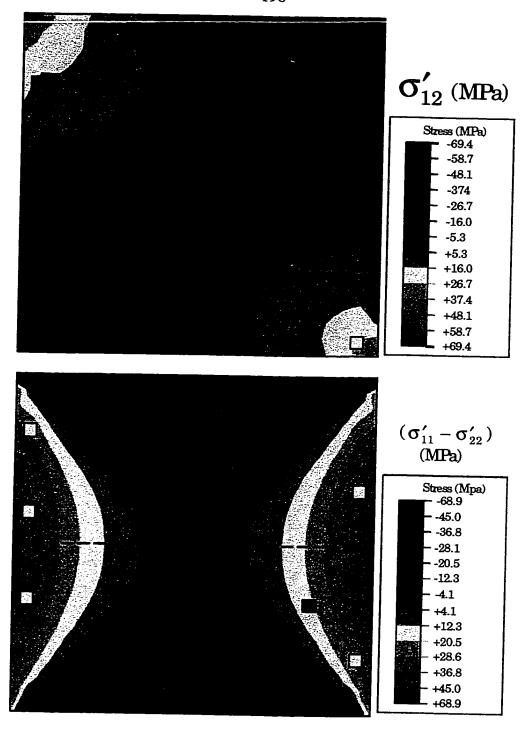

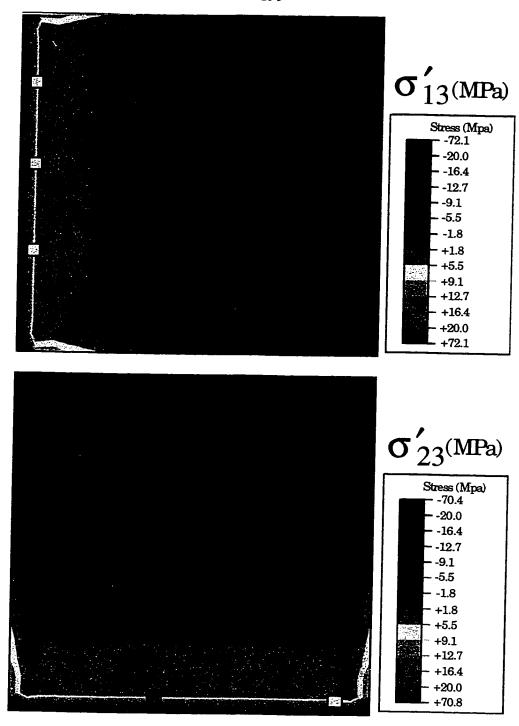

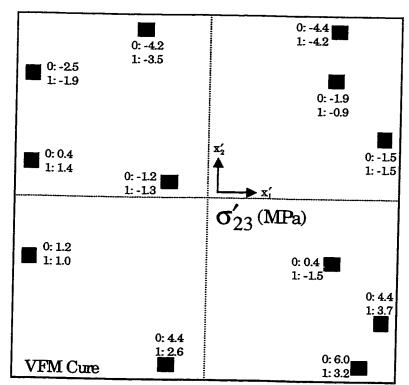

| 8.15 | Finite Element Contours and Experimental Data (COB Study #2)                                  | 198 |

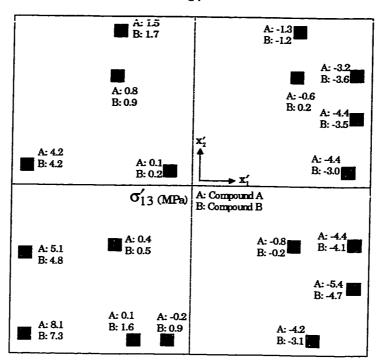

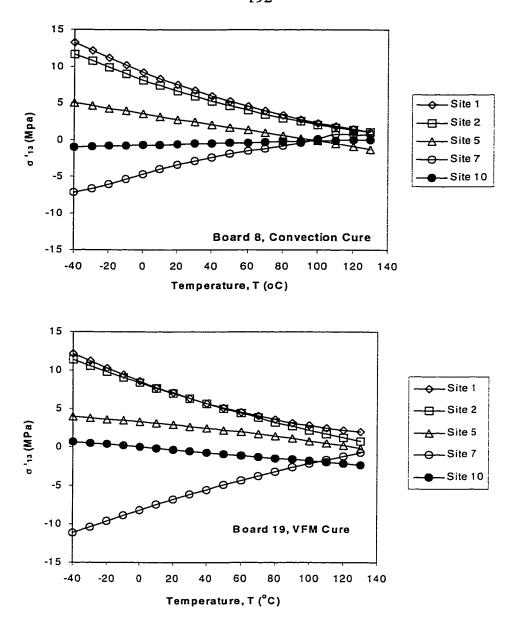

| 8.16 | Stress Variation Due to Thermal Cycling ( $\sigma'_{12}$ , COB Study #2)                      | 201 |

| 8.17 | Stress Variation Due to Thermal Cycling $(\sigma'_{11} - \sigma'_{22}, COB \text{ Study #2})$ | 202 |

| 8.18 | Stress Variation Due to Thermal Cycling ( $\sigma'_{13}$ , COB Study #2)                      | 203 |

| 8.19 | Stress Variation Due to Thermal Cycling ( $\sigma'_{23}$ , COB Study #2)                      | 204 |

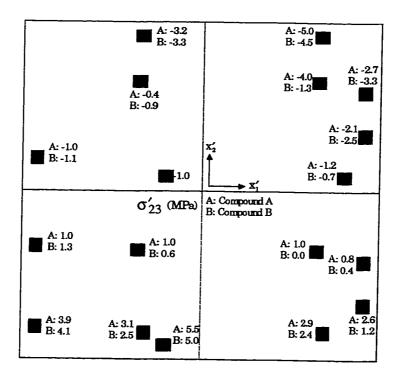

| 8.20 | Stress Variation Due to High Humidity Storage ( $\sigma'_{12}$ , COB Study #2)                                        | 206 |

|------|-----------------------------------------------------------------------------------------------------------------------|-----|

| 8.21 | Stress Variation Due to High Humidity Storage ( $\sigma'_{11} - \sigma'_{22}$ , COB Study #2)                         | 207 |

| 8.22 | Stress Variation Due to High Humidity Storage ( $\sigma'_{13}$ , COB Study #2)                                        | 208 |

| 8.23 | Stress Variation Due to High Humidity Storage ( $\sigma'_{23}$ , COB Study #2)                                        | 209 |

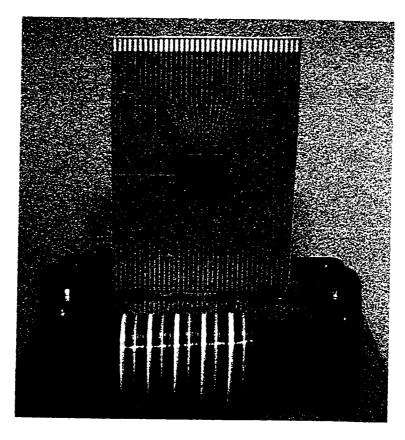

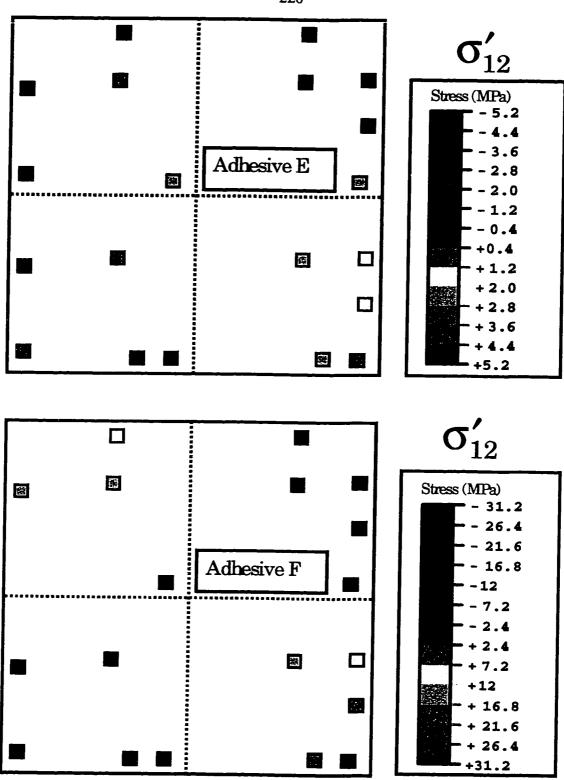

| 9.1  | Typical Ceramic 281 Pin PGA Package with Attached Test Chip                                                           | 215 |

| 9.2  | Sensor Rosette Locations (400 x 400 mil Test Chip, PGA Study)                                                         | 216 |

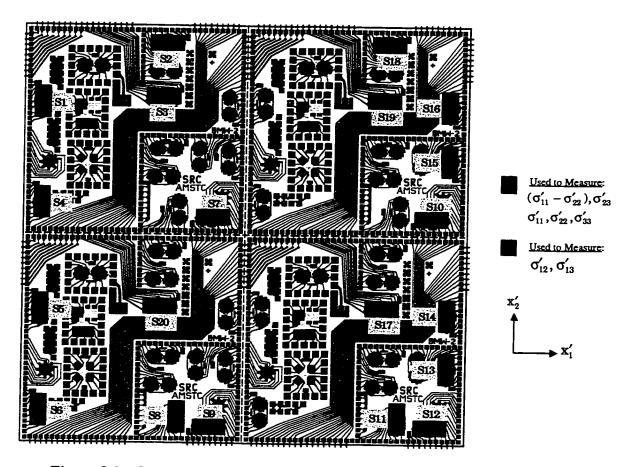

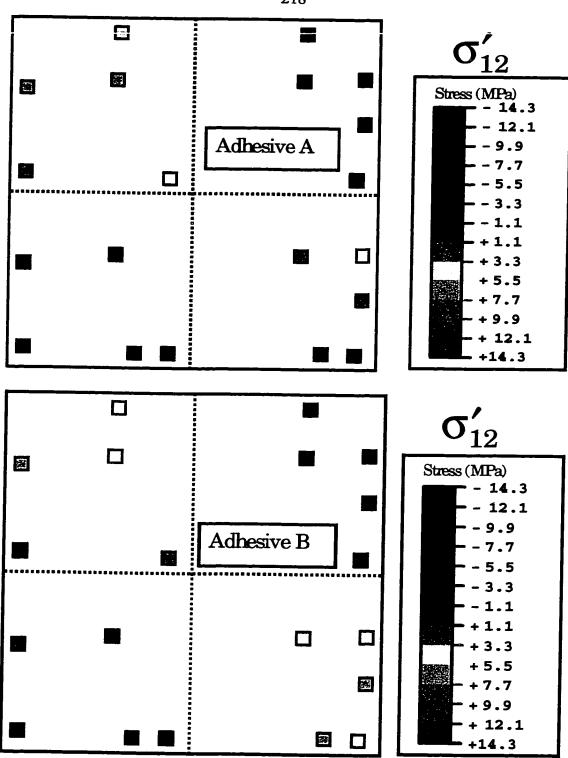

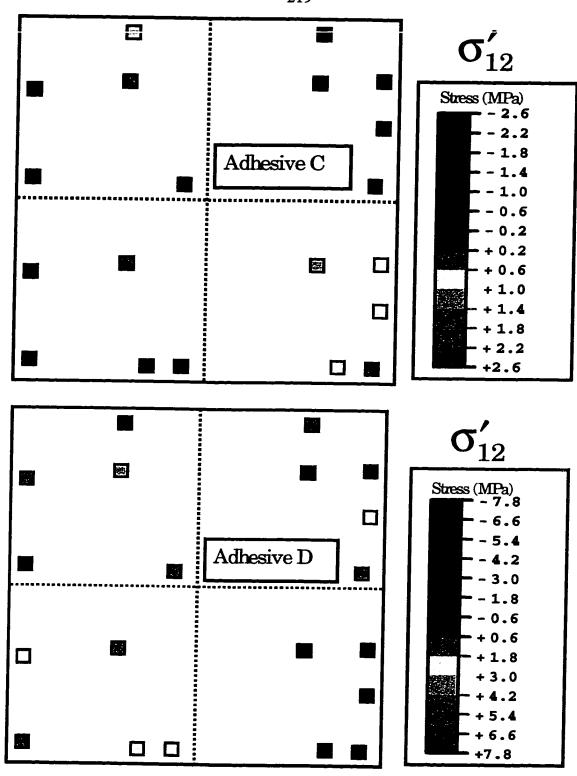

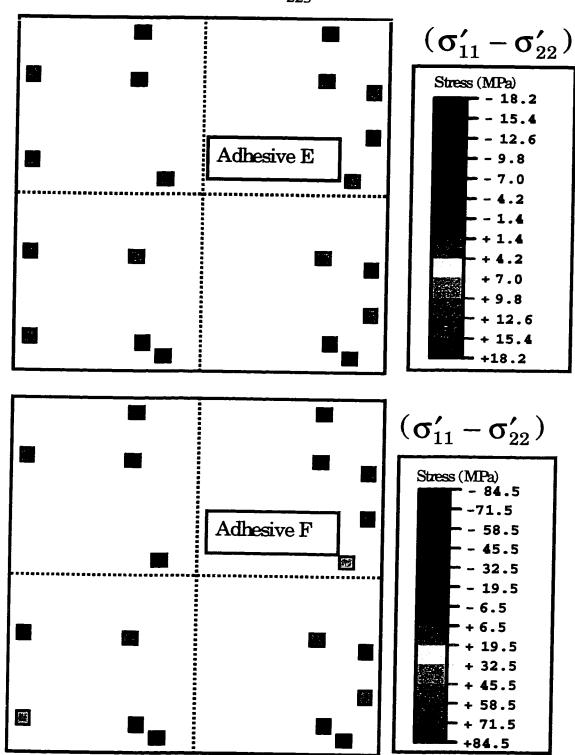

| 9.3  | Measured In-Plane Shear Stress Distributions (PGA Study)                                                              | 218 |

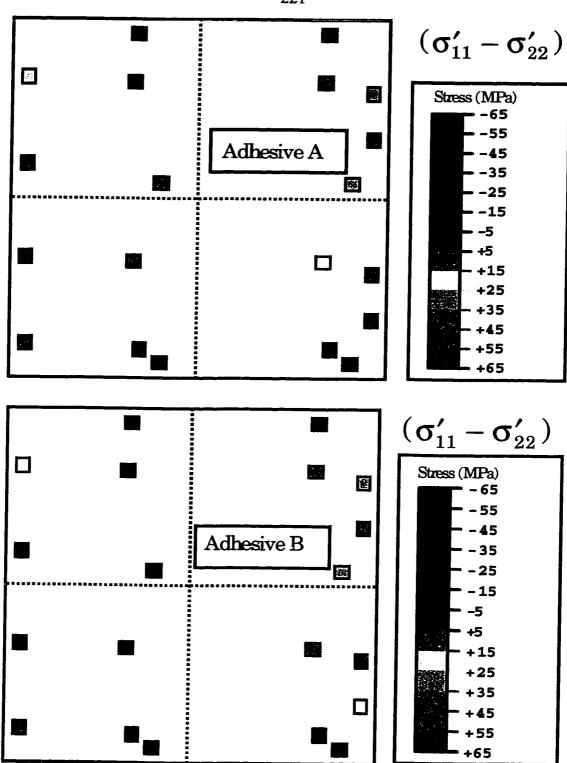

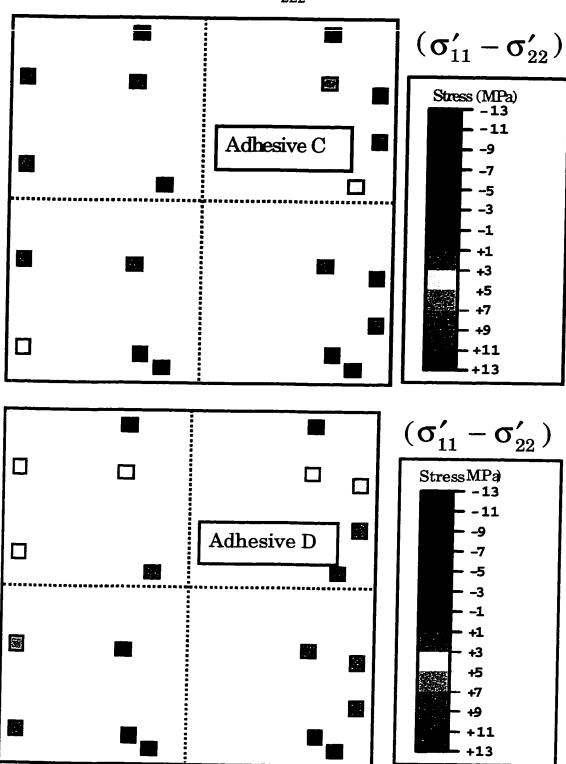

| 9.4  | Measured In-Plane Normal Stress Difference Distributions (PGA Study)                                                  | 221 |

| 9.5  | Finite Element Mesh for the PGA Package (One Quarter Model)                                                           | 220 |

| 9.6  | In-Plane Shear Stress Contour Maps Predicted by Finite Element Analysis and Experimental Data (PGA Study)             | 226 |

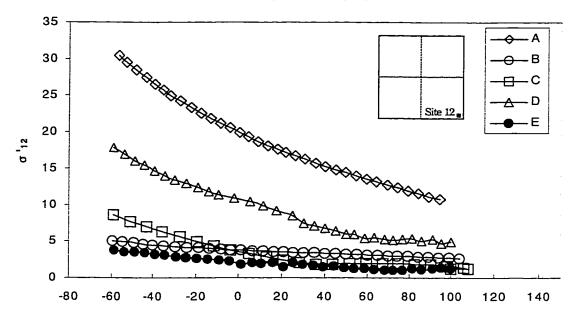

| 9.7  | In-Plane Normal Stress Difference Contour Maps Predicted by Finite Element Analysis and Experimental Data (PGA Study) | 227 |

| 9.8  | Variation of Die Attachment Stress with Temperature                                                                   |     |

|      | (PGA Study, Sensor at Site 12)                                                                                        | 230 |

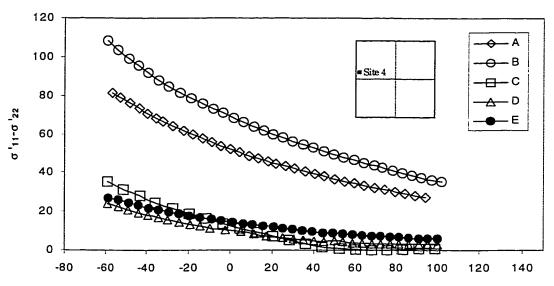

| 9.9  | Variation of Die Attachment Stress with Temperature                                                                   |     |

|      | (PGA Study, Sensor at Site 4)                                                                                         | 230 |

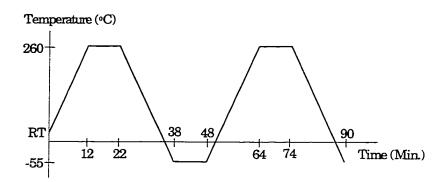

| 9.10 | Thermal Cycling Temperature profile                                                                                   | 232 |

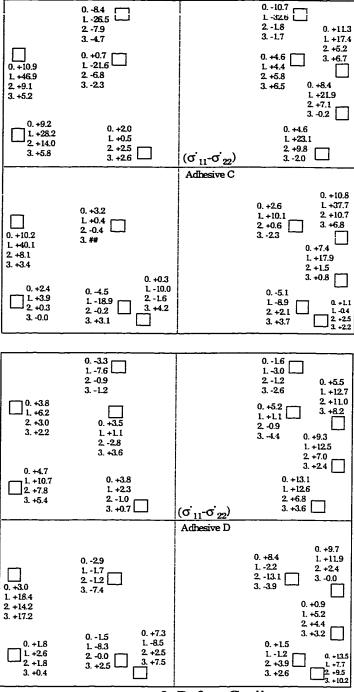

| 9.11 | Effects of Thermal Aging on Die Surface Stresses (In-Plane Normal Stress Difference in MPa, PGA Study)                | 234 |

| 9.12 | Effects of Thermal Aging on Die Surface Stresses (In-Plane Shear Stress in MPa, PGA Study)                            | 237 |

| 9.13 | Typical Cracking and Delamination of a Die Attachment<br>Adhesive after Reliability Testing                           | 240 |

| 9.14 | Effects of Thermal Cycling on Die Surface Stresses                                                                    |     |

|      | (In-Plane Normal Stress Difference in MPa, PGA Study) | 242 |

|------|-------------------------------------------------------|-----|

| 9.15 | Effects of Thermal Cycling on Die Surface Stresses    |     |

|      | (In-Plane Shear Stress in MPa, PGA Study)             | 245 |

## LIST OF TABLES

| 4.1 | Piezoresistive Coefficient Calibration Results (BMW-1)                     | 46  |

|-----|----------------------------------------------------------------------------|-----|

| 4.2 | Piezoresistive Coefficient Calibration Results (BMW2.1)                    | 49  |

| 4.3 | Piezoresistive Coefficient Calibration Results (BMW2.2)                    | 49  |

| 4.4 | Piezoresistive Coefficient Calibration Results (BMW2.3)                    | 50  |

| 4.5 | Connection between Bonding Pads and Channels In a Bank of One Card         | 68  |

| 5.1 | Molding Compound Properties (44 Pin PLCC)                                  | 76  |

| 5.2 | Material Properties (160 Pin QFP)                                          | 84  |

| 5.3 | Average Measurement Stresses at Selected Locations With Standard Deviation | 89  |

| 6.1 | Room Temperature Isotropic Properties                                      | 106 |

| 6.2 | Average Measurement Stresses at Selected Locations With Standard Deviation | 115 |

| 6.3 | Material Properties for the 240 Pin QFP (BMW-2 Study)                      | 116 |

| 6.4 | Delaminated Regions in the Encapsulated BMW-1 Test Chips                   | 122 |

| 7.1 | Material Properties for COB Die Attachment Model                           | 143 |

| 7.2 | Hysol FP4450 Properties                                                    | 165 |

| 8.1 | Temperature Dependent Material properties of Hysol FP4651                  | 194 |

| 9.1 | Die Attachment Materials and Properties                                    | 214 |

| 9.2 | Maximum Stress Values at Room Temperature (MPa)                            | 224 |

xviii

| 9.3 | Evaluation of the Die Attachment Adhesives under Thermal Aging Reliability Tests   | 248 |

|-----|------------------------------------------------------------------------------------|-----|

| 9.4 | Evaluation of the Die Attachment Adhesives under Thermal Cycling Reliability Tests | 248 |

#### CHAPTER 1

#### INTRODUCTION

Stresses due to thermal and mechanical loadings are often produced in chips which are incorporated into electronic packages. During fabrication steps such as encapsulation and die attachment, thermally-induced stresses are created. These occur due to non-uniform thermal expansions resulting from mismatches between the coefficients of thermal expansion of the materials comprising the package and the semiconductor die. Additional thermally-induced stresses can be produced from heat dissipated by high power density devices during operation. Finally, mechanical loading can be transmitted to the package through contact with the printed circuit board to which it is mounted. The combination of all of the above loadings can lead to two-dimensional (biaxial) and three-dimensional (triaxial) states of stress on the surface of the die. If high-power density devices within the package are switched on and off, these stress states can be cyclic in time causing fatigue loading. All of these factors can lead to premature failure of the package such as fracture of the die, severing of bond connections, die attach failure, and encapsulant cracking. These reliability problems are of ever increasing concern as larger scale chips and higher temperature applications are considered.

Stress analyses of electronic packages and their components have been performed using analytical, numerical, and experimental methods. Analytical investigations have been primarily concerned with finding closed-form elasticity solutions for layered

structures, while numerical studies have typically considered finite element solutions for sophisticated package geometries. Experimental approaches have included the use of test chips incorporating piezoresistive stress sensors (semiconductor strain gages), and the use of optical techniques such as holographic interferometry, moiré interferometry, and photoelasticity.

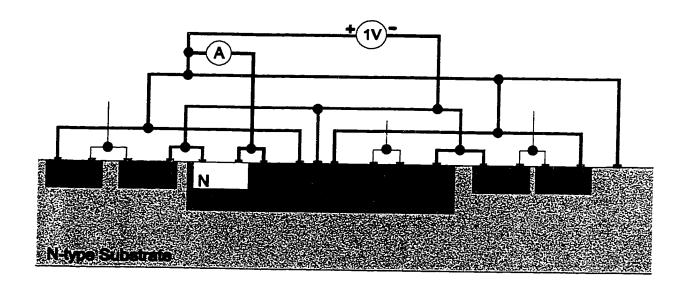

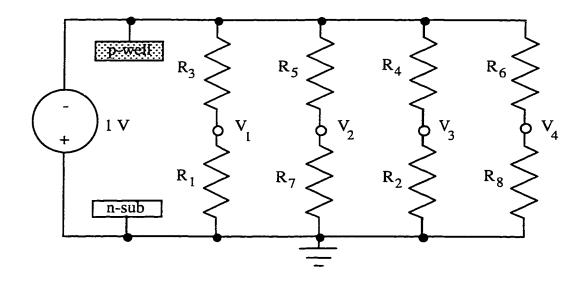

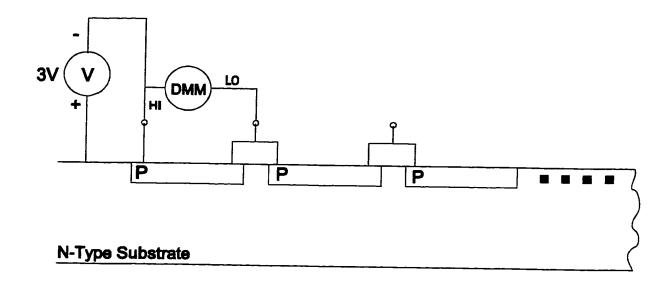

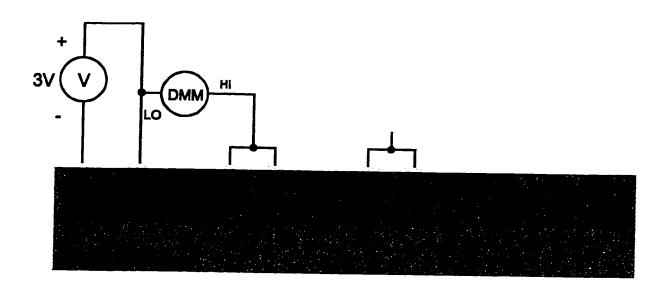

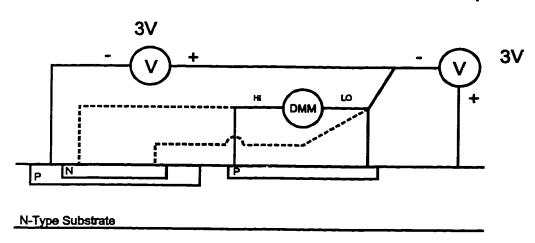

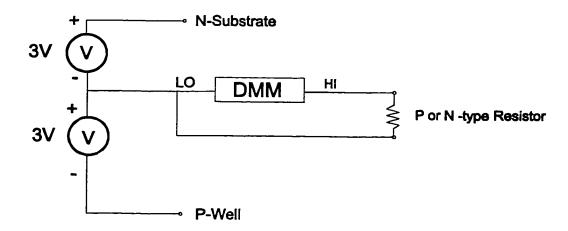

Piezoresistive stress sensors are a powerful tool for experimental structural analysis of electronic packages. Figure 1 illustrates the basic application concepts. The structures of interest are semiconductor (e. g. silicon) chips which are incorporated into electronic packages. The sensors are resistors which are conveniently fabricated into the surface of the die using current microelectronic technology. The sensors are not mounted on the chips. Rather, they are an integral part of the structure (chip) to be analyzed by the way of the fabrication process. The stresses in the chip produce resistance changes in the sensors (due to the piezoresistive effect) that can be measured. Therefore, the sensors are capable of providing non-intrusive measurements of surface stress states on a chip even within encapsulated packages (where they are embedded sensors). If the piezoresistive sensors are calibrated over a wide temperature range, thermally-induced stresses can be measured. Finally, a full-field mapping of the stress distribution over the surface of a die can be obtained using specially designed test chips which incorporate an array of sensor rosettes.

Prior publications on stress sensing test chips have included sensor rosettes with up to eight resistors. Using n-type and p-type sensors at various orientations, several or all the stress components on the die surface can be measured. By monitoring packaging stresses using stress sensing test chips, a variety of accomplishments have been achieved. For instance, test chips have been used to provide a better understanding of the shear stress

Figure 1.1 – Piezoresistive Sensor Concept

failure mechanisms in plastic packages. In addition, thermal stresses due to die attachment, molding, and temperature variation have been characterized. The effects of die size and package configuration on the stresses after molding have also been quantified for various package pin counts. Piezoresistive measurements have allowed molding compound materials to be evaluated with respect to their thermal-induced stress levels. Also, the effects of thermal cycling and delamination at the chip/encapsulant interface can be explored using test chips. Recently, thermal stress measurements of epoxy underfilled flip-chip on board devices were reported, and the effects of the curing conditions of the underfills were investigated.

Theoretical analysis has established that properly designed sensor rosettes on the (111) silicon wafer plane have several advantages relative to sensors fabricated using standard (100) silicon. In particular, optimized rosettes on (111) silicon can be used to measure the complete state of stress (six stress components) at a point on the top surface of the die, while optimized rosettes on (100) silicon can measure at most four stress components. Also, optimized sensors on (111) silicon offer the unique capability of measuring four temperature compensated combined stress components, while those on (100) silicon can only be used to measure two temperature compensated quantities. Furthermore, it has been established that the (111) plane offers the opportunity to measure the highest number of stress components in a temperature compensated manner. This is particularly important, given the large thermally induced errors which can often be found in stress sensor data. The four stress components which can be measured in a temperature compensated manner using (111) silicon sensors are the three shear stress components and the difference of the in-plane normal stress components.

In this work, (100) and (111) silicon test chips containing an array of optimized piezoresistive stress sensor rosettes, which were designed and fabricated in Auburn University, have been successfully applied within several electronic packaging configurations. Calibrated and characterized stress test chips were assembled into various packaging configurations. The post packaging resistances of the sensors were then recorded. These packaging resistances were monitored at room temperature, as a function of temperature excursion, or during long term packaging reliability qualification tests (thermal cycling and thermal aging). The stresses on the die surface were calculated using the measured resistance changes and the appropriate theoretical equations. For comparison purpose, three-dimensional nonlinear finite element simulations of the plastic encapsulated packages were also performed, and the stress predictions were correlated with the experimental test chip data.

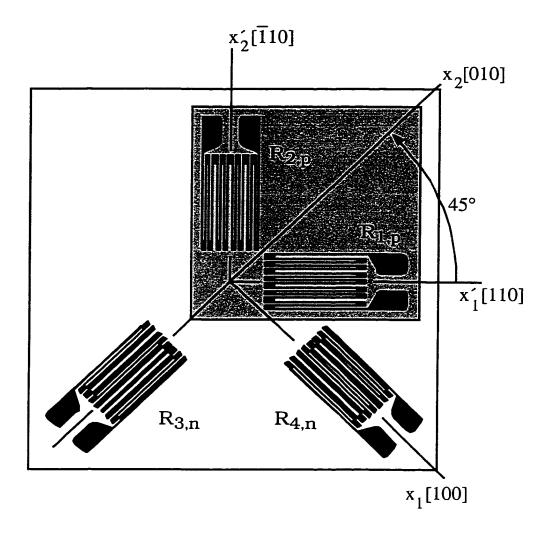

Silicon piezoresistive theory has been reviewed to allow for understanding of the equations utilized for stress calculation on the die surface. General resistance change equations were expressed in the unprimed crystallographic system, and in an arbitrarily rotated primed coordinate system. The ensuing resistance change equations for (100) and (111) silicon wafer planes were then extracted. The (100) silicon test chip (AAA-2) utilized in this work incorporates an array of optimized four-element dual polarity sensor rosettes for stress measurements. Each of these rosettes contains a 0-90° p-type resistor pair and a  $\pm 45^{\circ}$  n-type resistor pair. It has been demonstrated that this choice of sensor orientations minimizes thermally induced errors as well as those due to resistor misalignment, maximizes stress sensitivity, and permits accurate temperature compensated measurement of the values of in-plane normal stress difference ( $\sigma'_{11} - \sigma'_{22}$ ) and the in-plane

shear stress  $\sigma'_{12}$ . The (111) silicon test chips (BMW-1 or BMW-2) used in this study contain p-type and n-type sensor sets, each with resistor elements making angles of  $\Phi$ =0,  $\pm$ 45, 90° with respect to  $x'_1$ -axis perpendicular to the wafer flat. This eight-element dual polarity rosette has been optimized to measure all six stress components (four in a temperature compensated manner). This is a particularly important attribute, given the large errors which can be introduced into non-temperature compensated stress sensor data when the temperature change T is not precisely known. The four measurable temperature compensated stress components are  $(\sigma'_{11} - \sigma'_{22})$ ,  $\sigma'_{12}$ ,  $\sigma'_{13}$ ,  $\sigma'_{23}$ .

The AAA-2 (100) silicon test chips containing optimized four-element dual polarity rosettes have been applied within plastic electronic packaging configurations including 44 pin Plastic Leaded Chip Carrier (PLCC) packages and 240 pin Quad Flat Packs (QFP's). In the PLCC stress studies, 100 x 100 mil test chips were encapsulated. Several molding compounds were considered and the stress levels were compared. Larger 450 x 450 mil AAA-2 test chips were used in 240 pin QFP's. No delaminations between the die surface and encapsulant occurred, and these measurement results then served as a reference for subsequent stress evaluations within delaminated QFP's. For all the packaging configurations, three-dimensional nonlinear finite element simulations were performed to correlate with the experimental results.

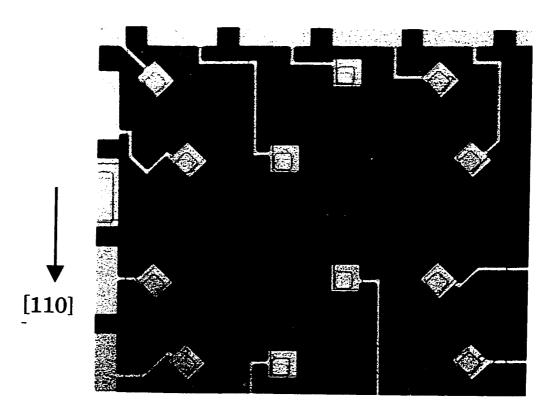

Advanced (111) silicon test chips (BMW-1 or BMW-2) comprising an array of optimized eight-element dual polarity piezoresistive sensor rosettes played a key role in recent stress assessments. Chips with dimensions of 400 x 400 mils were encapsulated in 240 pin QFP's, 160 pin QFP's, Chip on Board (COB) packages, and 281 pin ceramic Pin

Grid Array (PGA) packages. BMW-1 and BMW-2 test chips were used to characterize 240 pin QFP's, and the presence and extent of delaminations between the die surface and the encapsulant was explored using C-Mode Scanning Acoustic Microscopy (C-SAM). The stress distributions in delaminated packages were then compared with those in non-delaminated packages. Two different molding compounds were used in the stress measurements within 160 pin QFP's. The post molded room temperature stress results were then compared.

Die stresses in wire bonded COB packages were measured using BMW-2 silicon stress test chips encapsulated in two molding compounds. The stress sensing rosettes were characterized after die attachment, and throughout the cure cycle of the liquid encapsulant. Using the measured data and appropriate theoretical equations, the stresses at sites on the die surface have been calculated. Also, the packaged die stresses were studied as a function of temperature. After these investigations, additional COB package studies were performed. In this case, a comparison of COB stress levels with convection and variable frequency microwave encapsulant curing was carried out. Stress comparisons were made throughout the entire packaging processes. Thermal cycling and high humidity storage reliability tests were conducted on some of the COB samples. The stress variations were studied as a function of the number of thermal cycles, and with the duration of moisture absorption. The comparison of stress shifts occurring with the two encapsulant curing methods was then made.

High temperature die-attachment materials were evaluated by applying BMW2 test chips within 281 pin ceramic PGA packages. Six adhesives were utilized in these experiments including silver filled glasses, polyimide pastes, thermoplastic films, and gold

germanium. A comparison of die stresses at room temperature caused by the different die attachment materials has been made. The stresses on the die surface were also extracted as a function of temperature when a single thermal cycle was applied. In addition, thermal aging and thermal cycling tests were conducted on the PGA packages. The die attachment materials were evaluated by the stress changes occurring during these reliability tests.

Finally, nonlinear finite element simulations of the 240 pin QFP, 160 pin QFP, COB, and 281 pin ceramic PGA packages were performed, and the predicted die stresses were correlated with the test chip measurements. Anisotropic (111) silicon material properties were used, while isotropic properties were assumed for materials other than silicon die. The materials were modeled as linear elastic with temperature dependent properties, and large deformations (kinematic nonlinearities) were utilized.

#### CHAPTER 2

#### LITERATURE REVIEW

Mechanical stresses are typically built into silicon device structures at virtually every stage of manufacture. Dale and Oldfield [1] addressed stress generation in packaging processes such as wafer preparation, oxidation, diffusion, metallization, die and wire bonding, encapsulation, and curing. Lau [2] has discussed several problems associated with stress, including package cracking, wire damage, and thin film cracking on the die. Stress generation mechanisms were also discussed with respect to die attachment, encapsulation, surface mounting processes, and bending during application. Nguyen [3] has presented current reliability issues involved with typical postmold IC packages. One of the four major concerns is stress. Issues such as stress mechanisms and measurement were reviewed.

The trend towards high integration of circuits has given rise to rapidly increasing stress fields in plastic packages because of the mismatches of the thermal expansion coefficients of dissimilar packaging materials. Mechanical and electrical failures due to induced thermal stresses have been documented since the 1970's. Within a plastic package, out-of-plane shear stresses act on the chip surface with the traction direction toward the center of the chip, causing deformation of the die metallization. With chips coated with passivation glass, these deformations can cause passivation cracking.

Microcracks in the plastic encapsulant or delamination at the die-encapsulant interface promote metal deformation, since they reduce the restrictions on plastic movement at the chip surface [4-8]. Isagawa, et al. [4] observed the deformation of aluminum metallization during thermal shock tests of plastic packages. The deformations were related to encapsulant properties, chip size, test temperature range, etc. Thomas [5] performed thermal cycling on molded packages containing unpassivated test chips. Lundström and Gustafsson [6], Lesk, et al. [7], and Edwards, et al. [8] also described metal shift or damage during thermal shock or thermal cycling tests.

Shear stresses are heavily concentrated at the corners and edges of the silicon die, and can result in thin film brittle passivation cracking or interlayer dielectric film cracking [9-15]. Okikawa, et al. [9-10] and Shirley, et al. [11] presented studies of thin film cracks due to thermal stresses. Foehringer, et al. [12] described a model which explained the interactions among the key variables related to thin film cracking. The effort to model the failure rate as a function of environmental stress severity was done by Blish and Vaney [13]. A special test chip was designed by Gee, et al. [14] to detect thin film cracking in PLCC packages with various pin counts, die sizes, thermal cycling numbers, etc. Inayoshi [15] demonstrated that stresses can disrupt the chip passivation, permitting moisture to penetrate through to the underlying aluminum metallization causing corrosion.

Delamination at the chip-encapsulant interface is believed to be the result of critical shear stresses on the die surface, and usually occurs during reliability tests, such as temperature cycling and Highly Accelerated Stress Testing (HAST). The

delaminations typically start at the corners of the silicon die, and proceed toward the chip center [16-23]. Nishimura, et al. [16] confirmed the delamination at the die-encapsulant interface using ultrasonic inspection techniques. Doorselaer, et al. [17] revealed the relation between electrical failures and delamination. Moore, et al. [18-20] applied C-SAM (C-Mode Scanning Acoustic Microscopy) technique to inspect delaminations and cracks in IC packages. The evaluations were performed with various molding compounds, lead frame finishes, and die surface conditions. A comparison of delamination effects between temperature cycling and HAST tests was carried out by van Gestel, et al. [21-22]. Delaminations at the chip-encapsulant interface of 240 pin QFP packages were also found by Zou, et al. [23] even before reliability tests. Interfacial adhesion is one of the key factors to achieve delamination free packaging. Evaluations of various interfaces in plastic packages were conducted by Nguyen, et al. [24-26].

The occurrence of microcracks in the encapsulant is another serious reliability issue with plastic packages. The microcracks usually initiate at the chip edges, then propagate into the encapsulant at roughly a 135° angle from the chip surface [5]. Thermal cycling between -55°C and 150°C was performed on Dual Inline Packages by Nishimura, et al. [16, 27]. Package cracking was observed as a function of the number of temperature cycles for different encapsulant and lead frame materials. The presence of microcracks in the encapsulant dramatically changes the stress distribution in a package. A tentative model was proposed by Schroen, et al. [28] to describe the stress relief and oscillation measurements during temperature cycling tests. The stresses causing the cracks are so high that may cut through silica filler particles [7]. To avoid high stress,

suggestions such as development of plastic encapsulants with low CTE, low elasticity modulus, high strength, optimized plastic curing processes, and prevention of moisture absorption, have been proposed or practiced [28-31].

Large residual stresses introduced during packaging procedures, especially die attachment and encapsulation steps, can also cause die cracks. Since silicon is an extremely brittle material, minor surface flaws can act as crack starters in the presence of tensile stresses [32, 33]. Improper dicing of silicon wafers is another contributor to die cracking [1].

Electronic characteristic changes occur in IC chips due to mechanical stresses introduced by packaging processes. The resistivity of diffused resistors shifts due to piezoresistive effects, so that piezoresistive stress sensors can be developed [34-36]. Other device characteristics shifts were also experimentally studied, or observed in actual plastic packaged devices [37-45]. Using the relations between MOS drain current change and the acting stresses, stress sensors based on piezoresistive field effect transistors (PIFET's) were proposed and designed [43-45].

To understand the stress developed in plastic packages during packaging processes, reliability tests, and actual applications, researchers have performed stress analyses using analytical, numerical, and experimental methodologies.

Suhir [46-49] and Liew, et al. [50] suggested analytical methods for evaluation of the interfacial stresses in bimetal thermostats based on elementary beam (or long-and-narrow plate) theory. Tay, et al. [51-53] discussed the mechanics of interfacial delamination, and presented analytical methods to describe moisture-induced

delamination growth during solder reflow. These analytical models were correlated with experimental observations to help understand failure mechanisms.

Finite element simulations provide useful insight into the stress distributions produced in plastic packages during die attachment, encapsulation, and reliability tests. Various package configurations, packaging material combinations, and conditions related to package processes and reliability tests can be investigated by means of finite element methods [54-67]. In early finite element modeling, Groothuis, et al. [54] and Pendse [55] displayed the effects of material choices and structure changes on stress variation within a DIP package. Kelly, et al. [56-59] demonstrated how thermal stresses are developed within a plastic package, and suggested innovations in processes such as a side buffer of soft material, etc. Mertol [60] studied the thermal stresses in a high pin count POFPs.

In two-dimensional finite element simulations of plastic packages, plane strain analyses would be more suitable for prismatic bodies (DIPs and SOPs), while packages with square features (PLCC, PQFP) could be represented by coaxial rings using axisymetric analyses [3]. van Gestel, et al. [61] used three layers of special interface elements to simulate delamination behavior when plastic packages were subjected thermal cycling. Sweet, et al. [62], applied a linear viscoelastic model to predict die surface stresses. Effects of various delamination conditions to die surface stress distributions were also evaluated. Liu, et al. [63-64] built finite element models to predict thermal deformation and delamination in PQFP's and made comparison with moiré interferometry testing data. Yeung, et al. [65] and Park, et al. [66] used finite

element analysis to evaluate the thermal residual stress in a PQFP assuming viscoelastic stress-strain behavior of the molding compounds.

Analytical solutions are difficult to achieve for complex packaging configurations. Although the finite element method (FEM) is a reliable modeling tool to predict stress distributions within packages, the computational results have to be verified by experimental analysis. In addition, finite element simulations are limited by the availability of packaging material properties, accurate understanding of packaging processes, and other assumptions and approximations. Thus, it is desirable to develop experimental stress analysis methods for electronic packages. Moiré interferometry was applied by Bastawros, et al. [67], Han and Guo [68], and Liu, et al. [63-64] to measure thermal deformations within packages. Shadow Moiré methods were effective in evaluating the warpage of packages [69-70]. Some other testing and measurement techniques were reviewed by Guo and Sarihan [71].

The piezoresistive effect is caused by the change of resistivity of semiconductors as a function of applied stresses. Smith [72] first proposed to use the piezoresistive behavior of semiconductors for stress and strain measurements. Since then, Tufte and Stezer [73] and Suhling, et al. [74-75] have investigated the temperature dependence of piezoresistive coefficients of silicon or germanium. Kanda [76] represented the piezoresistive coefficients graphically. Yamada, et al. [77] addressed the nonlinearity of the piezoresistive effect. Dally and Riley [78] discussed the properties and performance characteristics of semiconductor strain gauges. The detailed theory for silicon

piezoresistive sensors was derived by Bittle, et al. [35, 79], and Kang [80] developed piezoresistive theory for silicon on various wafer planes and for silicon carbide.

Piezoresistive sensors are a powerful tool for experimental structural analysis of electronic packages. The sensors are resistors which are conveniently fabricated into the surface of the die using current microelectronic technology, and are capable of providing non-intrusive measurements of surface stress state on a chip even within encapsulated packages [81-82].

Several investigators have used stress test chips based on piezoresistive sensors to examine die stresses in plastic encapsulated packages. In early studies, Edwards and coworkers [8, 28, 83-84], Groothuis, et al. [54], and van Kessel, et al. [32] used (100) silicon test chips based on 0-90 two-element sensor rosettes to examine stresses in small pin count packages. Resistance changes of sensors during thermal cycling and pressure cooker environment tests were compared [28]. Die stress studies were utilized to direct the selection of packaging materials and the control of packaging processes [83-84]. The mechanism of structure failures were also investigated [32, 42, 54].

Gee and co-workers [85-87] have mapped die surface stress distributions using (111) test chips containing an array of four element 0-±45-90° sensor rosettes. In these studies, tests were also performed to understand the effects of package geometrical parameters and thermal cycling on the die stress levels. Further investigations with these chips were performed on 40 pin dual in-line packages (DIP's) by van Gestel and coworkers [88-89]. In addition, Lead frames and molding compounds were studied by Lundström, et al. [6] using a (111) silicon test chip with p-type four-element rosettes.

Temperature dependent stress state measurements after die attachment and encapsulation were examined by Natarajan, et al. using n-type (100) silicon test chips [90].

Miura, et al. [91-94, 36, 39] have used (100) test chips incorporating fourelement dual-polarity rosettes (0-90° n-type resistors and ±45° p-type resistors) to characterize thermally-induced die stresses in DIP's. Their sensor rosette design was the first capable of measuring the out-of-plane normal stress perpendicular to the die surface. In one of these studies, the effects of internal structure on plastic packaging reliability were explored [93]. The level of die stress was studied as a function of temperature changes and thermal cycling tests [36]. Delamination at the interface of die/encapsulant was also correlated to varied stress magnitudes [39]. Zou, et al. [95] have recently used (100) test chips based on a similar rosette with reversed doping polarities (0-90° p-type resistors and ±45° n-type resistors) to characterize the stresses in plastic leaded chip carrier (PLCC) packages that were encapsulated using several different molding compounds. Sweet and co-workers [34, 62, 96-98] have used the (100) silicon Sandia ATC-04 test chip to investigate liquid encapsulation of integrated circuit die mounted directly on ceramic substrates, and to study 160 pin quad flat packs (QFP's). The ATC-04 contains a multiplexed array of sensor rosettes. Each dual-polarity rosette contains eight resistors (0-±45°-90° orientations for both p-type and n-type resistors).

Other experimental studies using test chips with piezoresistive stress sensors can be found in the literature [99-109]. Skipor, et al. [99] compared both stress measurements using test chips and displacement measurements using moiré interferometry with FEM calculations for 64 pin TQFP and 68 pin PLCC packages. Lo,

et al. [100-101] and Bossche, et al. [102-103] described the design, fabrication, and calibration of their own stress test chips. Ducos, et al. [104] presented the in-situ stress measurements during package assembly. Nysaether, et al. [105-106] examined the thermally-induced stresses in glob-on-top pressure sensor samples. Rey, et al. [107] associated creep of the solder joints in leaded components with stress measurements in the silicon die. They used experimental data together with the FEM simulations to find a mathematical model for creep in the solder. Palmer, et al. [108] attempted to measure the stress variation during plastic package molding. Sensor resistance measurements for test chips assembled into TBGA, MBGA, and ViperBGA<sup>TM</sup> packages were made by Thomas, et al. [109].

In recent applications of piezoresistive stress sensors, mechanical stresses in epoxy underfilled flip-chip on board packages were studied [110-114]. In-situ flip-chip assembly mechanical stress measurements using piezoresistive test chip were first reported by Peterson and co-workers [110]. In that work, die stresses were evaluated for several underfill materials. Nysæther, et al. [111] and Palaniappan, et al. [112] investigated the impact of curing parameters on the die stresses induced in flip-chip assembly processes. In reference [111], stress measurements were presented as a function of temperature when the underfill was cured at temperatures of 85 °C, 120 °C, and 150 °C. In reference [112], the residual die stresses were found to be strongly dependent on several underfill properties including CTE, storage modulus, T<sub>g</sub>, and ultimately the underfill cure process. The effect of the choice of encapsulation material on the stresses during underfill cure, and preliminary stress measurements during thermal

cycling were also reported by Palaniappan, et al. [113-114].

Theoretical analysis by Suhling and co-workers [35, 81-82, 115] has established that properly designed sensor rosettes on the (111) silicon wafer plane have several advantages relative to sensors fabricated using standard (100) silicon. Optimized rosettes on (111) silicon can be used to measure the complete state of stress (six stress components) at a point on the top surface of the die, and offer the unique capability of measuring four temperature compensated combined stress components. Suhling, et al. [81, 116] have used the (111) silicon BMW-1 test chip to make the first measurements of the complete state of stress (six stress components) on the surface of an encapsulated die. The BMW-1 chip incorporates dual-polarity eight element rosettes (0-±45°-90° orientations for both p-type and n-type resistors). In these studies, stresses were measured in chip on board (COB) packages where the test chips were bonded to FR-4 substrates and over-molded using "glob-top" liquid encapsulants. In addition to the inplane stress components measured in the above studies, the first measurements of out-ofplane (interfacial) shear stresses at the die to encapsulant interface were recorded. The majority of the measurements were made at room temperature, but a demonstration of the variation of the die surface stresses with package temperature was also made. Results were correlated with the predictions of finite element simulations.

The (111) silicon BMW-1 test chip was also applied by Zou, et al. [23] to detect delaminations at the interface of the die and encapsulant. The stress distributions on the die surface in delaminated packages were compared with those in non-delaminated packages. The (111) silicon BMW-2 test chip was utilized by Zou, et al. [117-121] to

characterize die surface stresses in various packaging configurations. The characterization of transient die stresses throughout the cure cycles of several chip-on-board (COB) encapsulants was performed [117-118]. High temperature die attachment adhesives were evaluated during thermal cycling and thermal aging tests in 281 pin Ceramic Pin Grid Array (CPGA) packages [119-120]. The comparison of die level stresses in COB packages processed with convection and variable frequency encapsulant curing were also made [121]. The experimental results were correlated to FEM simulations, and reasonable agreements were obtained [117-121]. Details of many of the above publications [23, 95, 117-121] are the subject of this dissertation.

Stress test chips need to be calibrated to obtain the piezoresistive coefficients required for the stress calculation. A four-point bending calibration procedure is typically used. Details of this method are discussed by Beaty, et al. [122], Bittle, et al. [35, 79], Suhling, et al. [74-75, 82], Jaeger, et al. [123-127] and van Gestal [89]. A wafer-level calibration technique was developed by Cordes [128] and Suhling, et al. [129-130]. A hydrostatic calibration method for (111) silicon test chips was developed and applied by Kang [80], and Suhling, et al. [82, 131].

An analysis of the errors associated with the design and calibration of piezoresistive stress sensors in (100) silicon has been made by Jaeger, et al. [132-133]. The significance of thermally induced errors in the calibration and application of silicon piezoresistive stress sensors was demonstrated by Jaeger, et al. [127]. A study on optimal temperature compensated piezoresistive stress sensor rosettes was presented by Suhling, et al. [115].

### CHAPTER 3

### REVIEW OF PIEZORESISTIVITY THEORY

# 3.1 General Resistance Change Equations

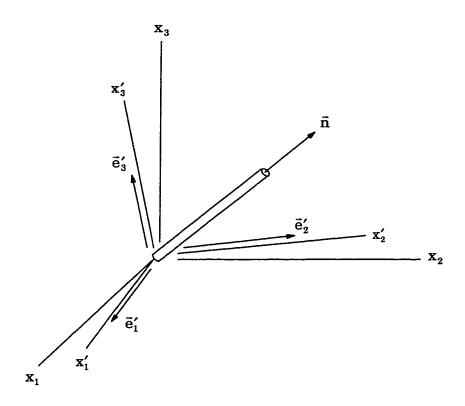

An arbitrarily oriented silicon filamentary conductor is shown in Figure 3.1. The unprimed axes  $x_1 = [100]$ ,  $x_2 = [010]$ , and  $x_3 = [001]$  are the principal crystallographic directions of the cubic (m3m) silicon crystal. The primed coordinate system is arbitrarily rotated with respect to this unprimed crystallographic system. For this conductor, the normalized change in resistance can be expressed in terms of the off-axis (primed) stress components using:

$$\frac{\Delta R}{R} = (\pi'_{1\alpha}\sigma'_{\alpha})l'^{2} + (\pi'_{2\alpha}\sigma'_{\alpha})m'^{2} + (\pi'_{3\alpha}\sigma'_{\alpha})n'^{2}

+ 2(\pi'_{4\alpha}\sigma'_{\alpha})l'n' + 2(\pi'_{5\alpha}\sigma'_{\alpha})m'n' + 2(\pi'_{6\alpha}\sigma'_{\alpha})l'm'

+ [\alpha_{1}T + \alpha_{2}T^{2} + ...]$$

(3.1)

where  $\pi'_{\alpha\beta}$  ( $\alpha,\beta=1,2,...,6$ ) are the off-axis temperature dependent piezoresistive coefficients,  $\alpha_1,\alpha_2,...$  are the temperature coefficients of resistance,  $T=T_m-T_{ref}$  is the difference between the measurement temperature and reference temperature (where the unstressed resistance R is measured), and I',m',n' are the direction cosines of the conductor orientation with respect to the  $x'_1,x'_2,x'_3$  axes, respectively [35, 80, 81, 115,]. In Eq. (3.1)

Figure 3.1 - Filamentary Silicon Conductor

and future indicial notation expressions, the summation convention is implied for repeated indices, and reduced index notation has been used for the stress components:

$$\sigma'_{1} = \sigma'_{11}, \ \sigma'_{2} = \sigma'_{22}, \ \sigma'_{3} = \sigma'_{33}

\sigma'_{4} = \sigma'_{13}, \ \sigma'_{5} = \sigma'_{23}, \ \sigma'_{6} = \sigma'_{12}$$

(3.2)

The 36 off-axis piezoresistive coefficients in Eq. (3.1) are related to the three unique on-axis piezoresistive coefficients  $\pi_{11}$ ,  $\pi_{12}$ ,  $\pi_{44}$  (evaluated in the unprimed coordinate system aligned with the crystallographic axes) using the transformation

$$\pi'_{\alpha\beta} = T_{\alpha\gamma}\pi_{\gamma\delta}T^{1}_{\delta\beta} \tag{3.3}$$

where

$$[\pi_{ij}] = \begin{bmatrix} \pi_{11} & \pi_{12} & \pi_{12} & 0 & 0 & 0 \\ \pi_{12} & \pi_{11} & \pi_{12} & 0 & 0 & 0 \\ \pi_{12} & \pi_{12} & \pi_{11} & 0 & 0 & 0 \\ 0 & 0 & 0 & \pi_{44} & 0 & 0 \\ 0 & 0 & 0 & 0 & \pi_{44} & 0 \\ 0 & 0 & 0 & 0 & 0 & \pi_{44} \end{bmatrix}$$

$$(3.4)$$

is the on-axis piezoresistive coefficient matrix, and

$$[T_{\alpha\beta}] = \begin{bmatrix} l_1^2 & m_1^2 & n_1^2 & 2 \, l_1 \, n_1 & 2 \, m_1 \, n_1 & 2 \, l_1 \, m_1 \\ l_2^2 & m_2^2 & n_2^2 & 2 \, l_2 \, n_2 & 2 \, m_2 \, n_2 & 2 \, l_2 \, m_2 \\ l_3^2 & m_3^2 & n_3^2 & 2 \, l_3 \, n_3 & 2 \, m_3 \, n_3 & 2 \, l_3 \, m_3 \\ l_1 \, l_3 & m_1 \, m_3 & n_1 \, n_3 & l_1 \, n_3 \, + \, l_3 \, n_1 & m_1 \, n_3 \, + \, m_3 \, n_1 & l_1 \, m_3 \, + \, l_3 \, m_1 \\ l_2 \, l_3 & m_2 \, m_3 & n_2 \, n_3 & l_2 \, n_3 \, + \, l_3 \, n_2 & m_2 \, n_3 \, + \, m_3 \, n_2 & l_2 \, m_3 \, + \, l_3 \, m_2 \\ l_1 \, l_2 & m_1 \, m_2 & n_1 \, n_2 & l_1 \, n_2 \, + \, l_2 \, n_1 & m_1 \, n_2 \, + \, m_2 \, n_1 & l_1 \, m_2 \, + \, l_2 \, m_1 \end{bmatrix}$$

$$(3.5)$$

is the six by six transformation matrix whose elements are related to the direction cosines of the primed coordinate directions with respect to the unprimed coordinate directions. The inverse of this transformation matrix can be expressed as:

$$[T_{\alpha\beta}]^{-1} = \begin{bmatrix} l_1^2 & l_2^2 & l_3^2 & 2l_1l_3 & 2l_2l_3 & 2l_1l_2 \\ m_1^2 & m_2^2 & m_3^2 & 2m_1m_3 & 2m_2m_3 & 2m_1m_2 \\ n_1^2 & n_2^2 & n_3^2 & 2n_1n_3 & 2n_2n_3 & 2n_1n_2 \\ l_1n_1 & l_2n_2 & l_3n_3 & l_1n_3 + l_3n_1 & l_2n_3 + l_3n_2 & l_1n_2 + l_2n_1 \\ m_1n_1 & m_2n_2 & m_3n_3 & m_1n_3 + m_3n_1 & m_2n_3 + m_3n_2 & m_1n_2 + m_2n_1 \\ l_1m_1 & l_2m_2 & l_3m_3 & l_1m_3 + l_3m_1 & l_2m_3 + l_3m_2 & l_1m_2 + l_2m_1 \end{bmatrix}$$

$$(3.6)$$

In Eqs. (3.5, 3.6), the direction cosines for the axes of the primed coordinate system are given by

$$\begin{bmatrix} a_{ij} \end{bmatrix} = \begin{bmatrix} a_{11} & a_{12} & a_{13} \\ a_{21} & a_{22} & a_{23} \\ a_{31} & a_{32} & a_{33} \end{bmatrix} = \begin{bmatrix} l_1 & m_1 & n_1 \\ l_2 & m_2 & n_2 \\ l_3 & m_3 & n_3 \end{bmatrix}$$

(3.7)

where

$$a_{ij} = \cos(x'_i, x_j) \tag{3.8}$$

When the primed axes are aligned with the unprimed (crystallographic) axes, the transformation matrix in Eq. (3.5) reduces to the 6 x 6 identity matrix. Thus, Eq. (3.3) reduces to

$$\pi'_{\alpha\beta} = \pi_{\alpha\beta} \tag{3.9}$$

and Eq. (3.1) simplifies to

$$\frac{\Delta R}{R} = [\pi_{11}\sigma_{11} + \pi_{12}(\sigma_{22} + \sigma_{33})]l^{2} + [\pi_{11}\sigma_{22} + \pi_{12}(\sigma_{11} + \sigma_{33})]m^{2}

+ [\pi_{11}\sigma_{33} + \pi_{12}(\sigma_{11} + \sigma_{22})]n^{2} + 2\pi_{44}[\sigma_{12}lm + \sigma_{13}ln + \sigma_{23}mn]

+ [\alpha_{1}T + \alpha_{2}T^{2} + ...]$$

(3.10)

where l, m, n are the direction cosines of the conductor orientation with respect to the unprimed (crystallographic) axes. Eq. (3.10) demonstrates that the resistance change of an arbitrarily oriented silicon resistor depends on all six stress components. As will be shown below, resistive sensor rosettes can be fabricated in certain silicon wafer planes which take advantage of this property and allow several stress components to be extracted from monitoring resistance changes.

# 3.2 Resistance Change Equations for Silicon Wafer Planes

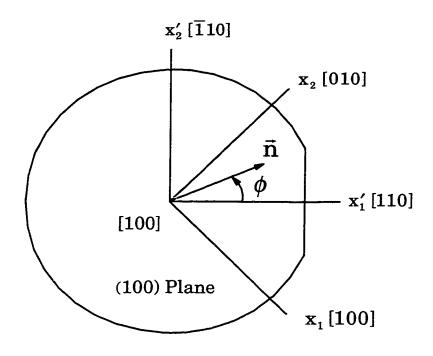

For a given wafer orientation, Eq. (3.1) can be used to obtain the resistance change equation for an arbitrarily oriented in-plane resistor. In the current microelectronics industry, it is most common for silicon devices to be fabricated using (100) silicon wafers. A general (100) silicon wafer is shown in Figure 3.2. The surface of the wafer is a (100) plane, and the [001] direction is normal to the wafer plane. The axes of the natural wafer coordinate system  $\mathbf{x}_1' = [110]$  and  $\mathbf{x}_2' = [\bar{1}10]$  are parallel and perpendicular to the primary wafer flat. To use Eq. (3.1), the off-axis piezoresistive coefficients in the primed coordinate system must be evaluated using Eq. (3.3) by substitution of the unprimed values in Eq. (3.4) and the appropriate direction cosines. For the unprimed and primed coordinate systems shown in Figure 3.2, the direction cosines are:

Figure 3.2 - (100) Silicon Wafer

$$[\mathbf{a}_{ij}] = \begin{bmatrix} \frac{1}{\sqrt{2}} & \frac{1}{\sqrt{2}} & 0\\ \frac{1}{\sqrt{2}} & \frac{1}{\sqrt{2}} & 0\\ 0 & 0 & 1 \end{bmatrix}$$

(3.11)

Substitution of the off-axis piezoresistive coefficients calculated in the manner described above into Eq. (3.1) yields

$$\frac{\Delta R}{R} = \left[ \left( \frac{\pi_{11} + \pi_{12} + \pi_{44}}{2} \right) \sigma'_{11} + \left( \frac{\pi_{11} + \pi_{12} - \pi_{44}}{2} \right) \sigma'_{22} \right] \cos^2 \phi

+ \left[ \left( \frac{\pi_{11} + \pi_{12} - \pi_{44}}{2} \right) \sigma'_{11} + \left( \frac{\pi_{11} + \pi_{12} + \pi_{44}}{2} \right) \sigma'_{22} \right] \sin^2 \phi

+ \pi_{12} \sigma'_{33} + (\pi_{11} - \pi_{12}) \sigma'_{12} \sin 2\phi + [\alpha_1 T + \alpha_2 T^2 + \dots]$$

(3.12)

where

$$l' = \cos\phi \quad m' = \sin\phi \quad n' = 0 \tag{3.13}$$

has been introduced, and  $\phi$  is the angle between the  $\chi'_1$ -axis and the resistor orientation. Equation (3.12) indicates that the out-of-plane shear stresses  $\sigma'_{13}$  and  $\sigma'_{23}$  do not influence the resistances of stress sensors fabricated on (100) wafers. This means that a sensor rosette on (100) silicon can at best measure four of the six unique components of the stress tensor. All three of the unique piezoresistive coefficients for silicon  $(\pi_{11}, \pi_{12}, \pi_{44})$  appear in Eq. (3.12). These parameters must be calibrated before stress component values can be extracted from resistance change measurements.

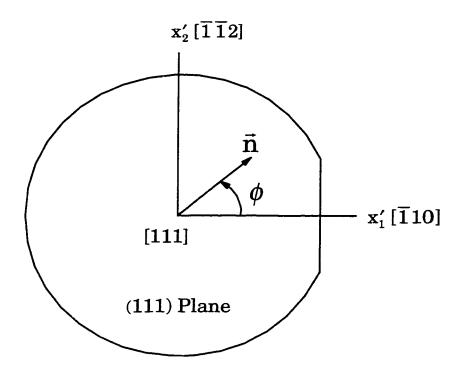

The other common silicon crystal orientation used in semiconductor fabrication is the (111) surface. A general (111) silicon wafer is shown in Figure 3.3. The surface of the wafer is a (111) plane, and the [111] direction is normal to the wafer plane. The principal crystallographic axes  $x_1 = [100]$ ,  $x_2 = [010]$ , and  $x_3 = [001]$  do not lie in the wafer plane and have not been indicated. As mentioned previously, it is convenient to work in an off-axis primed wafer coordinate system where the axes  $x'_1, x'_2$  are parallel and perpendicular to the primary wafer flat. Using Eq. (3.1), the resistance change of an arbitrarily oriented inplane sensor can be expressed in terms of the stress components resolved in this natural wafer coordinate system. The off-axis piezoresistive coefficients in the primed coordinate system must be first evaluated by substituting the unprimed values given in Eq. (3.4) and the appropriate direction cosines for the primed coordinate directions with respect to the unprimed (crystallographic) coordinate directions into the transformation relations given in Eq. (3.3). For the primed coordinate system indicated in Figure 3.3, the appropriate direction cosines for the primed axes are

$$[a_{ij}] = \begin{bmatrix} -\frac{1}{\sqrt{2}} & \frac{1}{\sqrt{2}} & 0 \\ -\frac{1}{\sqrt{6}} & -\frac{1}{\sqrt{6}} & \frac{2}{\sqrt{6}} \\ \frac{1}{\sqrt{3}} & \frac{1}{\sqrt{3}} & \frac{1}{\sqrt{3}} \end{bmatrix}$$

(3.14)

Substitution of the off-axis piezoresistive coefficients, calculated in the manner described above, into Eq. (3.1) yields

Figure 3.3 - (111) Silicon Wafer

$$\frac{\Delta R}{R} = [B_1 \sigma'_{11} + B_2 \sigma'_{22} + B_3 \sigma'_{33} + 2\sqrt{2}(B_2 - B_3)\sigma'_{23}]\cos^2 \phi

+ [B_2 \sigma'_{11} + B_1 \sigma'_{22} + B_3 \sigma'_{33} - 2\sqrt{2}(B_2 - B_3)\sigma'_{23}]\sin^2 \phi

+ [2\sqrt{2}(B_2 - B_3)\sigma'_{13} + (B_1 - B_2)\sigma'_{12}]\sin 2\phi

+ [\alpha_1 T + \alpha_2 T^2 + ...]$$

(3.15)

where  $\phi$  is again the angle between the  $x'_t$ -axis and the resistor orientation. The coefficients

$$B_{1} = \frac{\pi_{11} + \pi_{12} + \pi_{44}}{2}$$

$$B_{2} = \frac{\pi_{11} + 5\pi_{12} - \pi_{44}}{6}$$

$$B_{3} = \frac{\pi_{11} + 2\pi_{12} - \pi_{44}}{3}$$

(3.16)